224G SerDes IP

Filter

Compare

11

IP

from

3

vendors

(1

-

10)

-

224G SerDes PHY and controller for UALink for AI systems

- UALink, the standard for AI accelerator interconnects, facilitates this scalability by providing low-latency, high-bandwidth communication.

- As a member of the UALink Consortium, Cadence offers verified UALink IP subsystems, including controllers and silicon-proven PHYs, optimized for robust performance in both short and long-reach applications and delivering industry-leading power, performance, and area (PPA).

-

224G Ethernet PHY, TSMC N3P x1, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications

-

224G Ethernet PHY, TSMC N2P x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications

-

224G Ethernet PHY, Intel 18A x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications

-

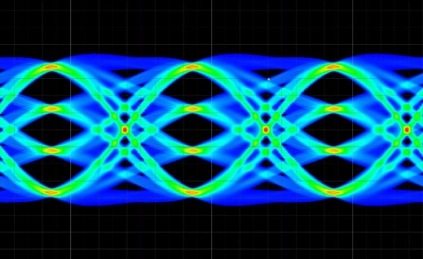

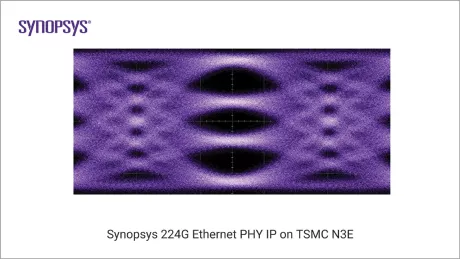

224G Ethernet PHY in TSMC (N3E)

- Optimized for performance, power, and area

- Includes one, two, or four full-duplex PAM-4/6 transceivers (transmit and receive functions)

- Supports IEEE and OIF-CEI-224G standards

- Includes auto-negotiation and link training capabilities

-

224G Ethernet PHY for TSMC 3nm

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

-

224G Ethernet PHY, TSMC N3E x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications

-

224G-LR SerDes PHY enables 1.6T and 800G networks

- Optimized Performance, Power and Area with Design Agility

- Supports full-duplex 1.25 to 225Gbps data rates

- Enables 1.6T, 800G, 400G, and 200G Ethernet with a PHY + Controller solution

- Supports evolving IEEE 802.3 and OIF-CEI-224G standard electrical specifications

- Meets the performance requirements of chip-to-module (VSR), chip-to-chip (MR), and copper/backplane (LR) interconnects

-

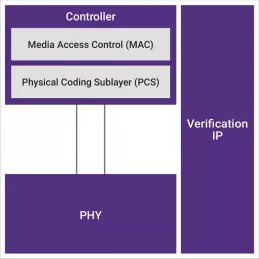

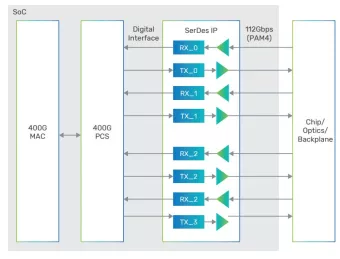

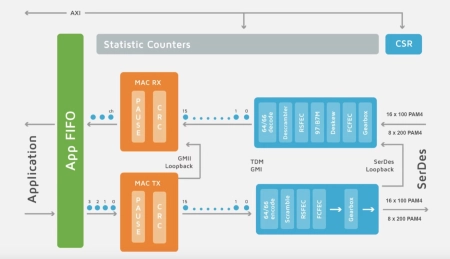

1.6T Ethernet UMAC

- Simple programming and bringing up sequence matching previous UMAC generations

- Support for arbitrary mixed modes across channels and dynamic mode switching

- Support for 224G SerDes

- Standard and priority pause generation, termination, and pass-through

- Support for jumbo frames up to 16K bytes

- TX runt frame padding and RX runt frame stripping

- Counters and interrupts for MIBs and various MAC and PCS/FEC events

-

1.6T Ethernet PCS IP

- Supports all required features of the IEEE 802.3 specification and draft specifications

- IP available in single 1.6T mode and quad channel mode supporting 4 x 400G, 2 x 800G and 1.6T

- Designed to be used with Synopsys 1.6T MAC IP for 1.6T Ethernet Systems

- Includes RS-FEC functions