112G serdes IP

Filter

Compare

8

IP

from

5

vendors

(1

-

8)

-

112G SerDes USR & XSR

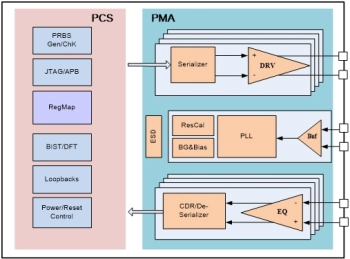

- 8 Channels per Macro, 2.5Gbps~112Gbps with TX/RX independent; NRZ Data Rate:2.5-56Gbps PAM4 Data Rates: 56-112Gbps

- Serialization/Deserialization interface width; PCS-User interface support 64bit in PIPE

- Two cascaded PLLs, one LC-tank based and the other ring-oscillator based

- Digitally-control-impedance termination resistors

-

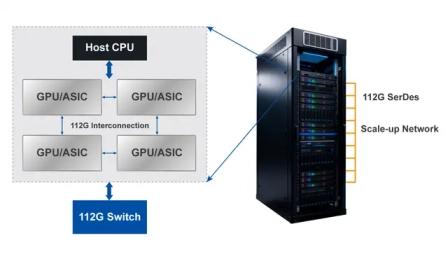

112G Multi-Rate SerDes

- Designed with a small footprint, ultra-low latency, and low power consumption, the 112G SerDes maximizes bidirectional memory access efficiency, reduces software complexity, and helps chip developers leverage existing Ethernet infrastructure to significantly lower Total Cost of Ownership (TCO).

- Featuring IEEE 802.3-compliant Forward Error Correction (FEC), 35dB ultra-high channel loss compensation, and adaptive high-speed equalization technologies (CTLE, FFE), it provides full-cycle link protection—from error correction to pre-warning—enabling highly compatible, stable, and efficient chip-to-chip connectivity solutions.

-

SerDes IP

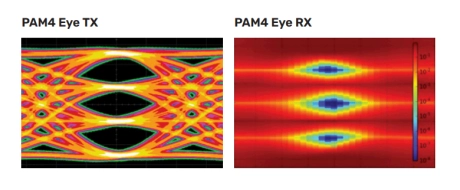

- 10dB to 35dB bump-to-bump insertion loss

- Multi-rate support for 56Gbps to 112Gbps PAM4 and NRZ

- Integrated PLL

- Robust clock distribution architecture

- Advanced mixed signal analog equalization architecture

- Fully adaptive and programmable RX equalization

- Auto-negotiation

- Link Training

-

112G-ULR PAM4 SerDes PHY

- Supports full-duplex 1.25Gbps to 112.5Gbps data rates

- Superior bit error rate (BER) performance across high-loss and reflective channels

- Compliant with IEEE 802.3ck and OIF standard electrical specifications

- Supports flexible SoC floorplan and IP placement and provides package substrate guideline/reference designs

-

112G Ethernet PHY in TSMC (N7, N5, N3P)

- Optimized for performance, power, and area

- Includes one, two, or four full-duplex PAM-4 transceivers (transmit and receive functions)

- Supports IEEE and OIF standards: IEEE 802.3ck, CEI-112G

- Includes auto-negotiation and link training capabilities – IEEE 802.3 clause 73

-

PHY for PCIe 7.0 and CXL

- Architecture optimized for HPC, AI/ML, storage, and networking

- Ultra-long reach, low latency, and low power

- Advanced DSP delivers unmatched performance and reliability

- Comprehensive real-time diagnostic, monitor, and test features

- Bifurcation support for x1, x2, x4, x8, and x16 lanes

-

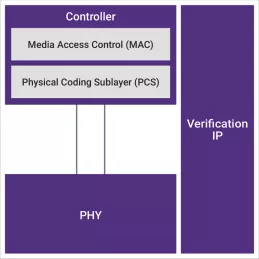

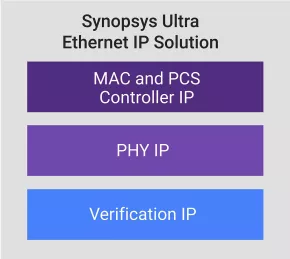

Complete 1.6T Ultra Ethernet IP Solution

- Ethernet MAC, PCS and PHY to complete a full Ultra Ethernet interface stack

- Supports evolving IEEE 802.3 and OIF-224G electrical standards

- Provides support for 4 x 400G, 2 x 800G, and 1.6T Ethernet rates using 112Gbps and 224Gbps SerDes

- Meets performance criteria for chip-to-chip, chip-to-module, and long reach copper/backplane interconnects

-

High Speed Ethernet 2/4/8-Lane 200G/400G PCS

- Compliant with the IEEE 802.3bs standard

- 400G PCS available in single, quad or octal port supporting multiple 100G/50G/25G/10G SerDes lanes

- 200G PCS available in single or quad port supporting multiple 100G/50G/25G/10G SerDes lanes

- Designed to be used with Synopsys 400G and 200G Ethernet MAC IP for 400G/200G Ethernet systems