10G Ethernet IP

Filter

Compare

130

IP

from

34

vendors

(1

-

10)

-

Low Latency Ethernet 10G MAC FPGA IP

- The Low Latency Ethernet 10G MAC FPGA IP core (soft IP) offers low round-trip latency, and an efficient resource footprint

- The Intellectual Property (IP) core offers programmability of various features listed

- This IP can be used in conjunction with the new Multi-Rate PHY FPGA IP core to support the range of 10M/100M/1G to 10G data rates.

-

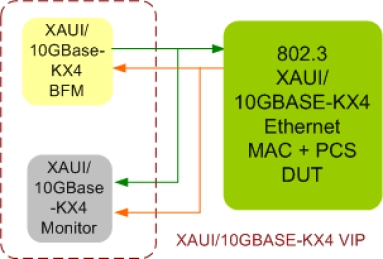

10G XAUI/10GBase-KX4 Ethernet Verification IP

- Follows 10G XAUI specification as defined in IEEE 802.3

- Follows 10Gbase-KX4 specification as defined in IEEE 802.3

- Supports backplane auto-negotation for 10GBASE-KX4

- Supports all types of 10G XAUI/10GBase-KX4 TX and RX errors insertion/detection.

-

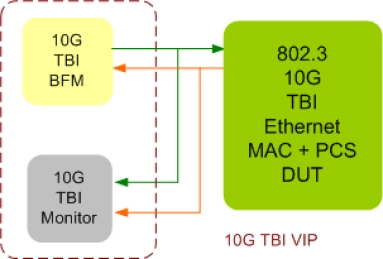

10G TBI (PCS) Ethernet Verification IP

- Follows 10G specification as defined in IEEE 802.3

- Supports all types of 8b/10b PCS TX and RX errors insertion/detection.

- Oversize, undersize, inrange, out of range Packet size errors

- Missing SPD/EPD/SFD framing errors

-

10G 64b/66b WIS Ethernet Verification IP

- Follows 10G specification as defined in IEEE 802.3ae.

- Supports all types of 64b/66b WIS TX and RX errors insertion/detection.

- Comes with 64b/66b WIS Tx BFM, 64b/66b WIS Rx BFM, and 64b/66b WIS Monitor

- Monitor supports detection of all protocol violations.

-

Ethernet 10G Verification IP

- Supports 10G as per specification IEEE 802.3-2018

- Supports XGMII(32 and 64 Width)

- Supports XGMII_R(32 and 64 Width)

- Supports XTBI (i.e Output of 8b/10b PCS)

-

High Speed Ethernet 10G to 100G TSN-MAC

- Supports all required features of the IEEE 802.3/802.3ba standard

- Supports IEEE standards for 10/25/40/50/100G Ethernet systems

- Supports IEEE 802.3br

- Two traffic classes for audio video bridging (AVB)

-

Low-Latency IP 10G Ethernet MAC

- LeWiz MAC tracks the Ethernet line for link detection

- On the receiving side, it:

- On the transmit side, it:

- Driver Support is available for Linux (Windows and others available based on customer request)

-

10G Ethernet TSN Subsystem

- 10G Ethernet MAC/PCS with 802.1CM (802.3br/802.1bu) preemption and interspersed express traffic feature for MAC+PCS/PMA

- Designed to the 25G Ethernet requirements for 10/25 Gb/s operation specified by IEEE 802.3 Clause 49, IEEE 802.3by, and the 25G Ethernet Consortium

- Low latency 64-bit 10G Ethernet MAC and BASE-R IP

- Allows multiple instantiations up to by 4

-

High Speed Ethernet Quad 10G to 100G PCS

- Compliant with the IEEE 802.3 standard

- Configurable IP available in single or quad port for speeds from 1G to 100G

- Designed to be used with Synopsys 100G Ethernet MAC IP for 100G Systems

- Integration tested with the Synopsys 100G Ethernet MAC IP and Synopsys 56G Ethernet PHY IP

-

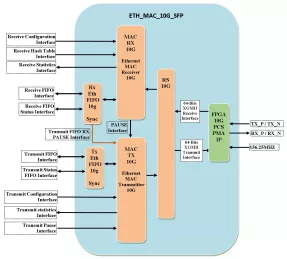

Ethernet MAC 10G SFP

- Transmit data FIFO interface to define the payload data

- Transmit Status FIFO interface to define if the CRC has to be append or to transmit a Error Control character