10/100/1000 Gigabit Ethernet PHY IP

Filter

Compare

14

IP

from

9

vendors

(1

-

10)

-

Gigabit Ethernet Controller

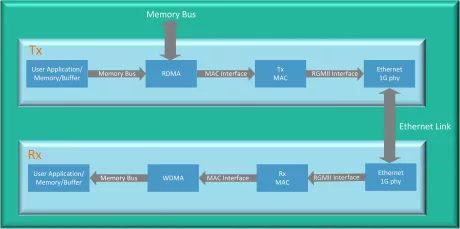

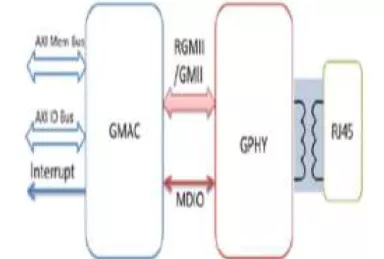

- XEC is a high performance 1000M/100M/10M Ethernet Controller IP. It support GMII/RGMII/MII/RMII MAC-PHY interface and support AXI/AHB system bus.

- XEC can receive the data from Ethernet PHY to the AXI/AHB bus, and to send out data from AXI/AHB bus to the Ethernet PHY.

-

Gigabit Ethernet MAC IP Core

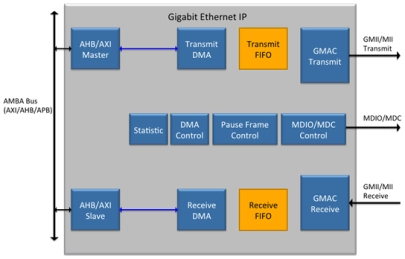

- The silicon-proven Gigabit Ethernet IP core provides a 10/100 Mbps Media Independent Interface (MII) and a 1000 Mbps Gigabit Media Independent Interface (GMII).

- It also supports optional Reduced MII (RGMII), and Serial GMII (SGMII).

-

Gigabit Ethernet with IEEE 1588 and AVB

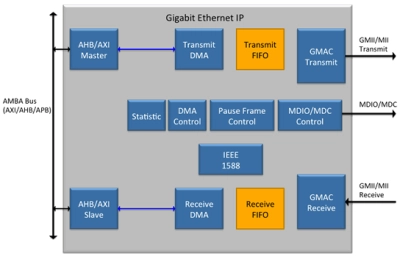

- The Gigabit Ethernet Media Access Controller IP is compliant with the Ethernet IEEE 802.3-2008 standard and supports protocol extensions for Audio Video Bridging (AVB).

- The Gigabit Ethernet IP provides a 10/100 Mbps Media Independent Interface (MII) and a 1000 Mbps Gigabit Media Independent Interface (GMII).

-

10/100/1000 Ethernet MAC DO-254 IP Core

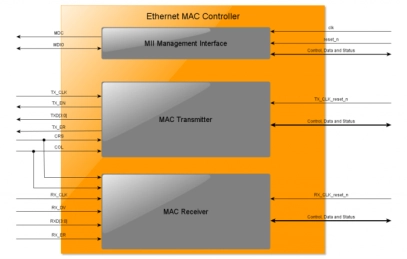

- The 10/100/1000 Ethernet MAC Controller DO-254 IP Core implements the Media Access Control as specified in the IEEE 802.3-2008 specification.

- The Ethernet MAC Controller has been developed to DAL A according to the DO-254 / ED-80 and is accompanied by a Certification Kit.

-

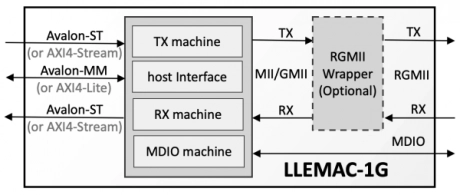

Low-Latency 10/100/1000 Ethernet MAC

- The LLEMAC-1G implements an Ethernet Media Access Controller (MAC) compatible with the 10/100 Mbps IEEE 802.3 and 1Gbps IEEE 802.3-2002 specifications.

- Featuring extremely low egress and ingress latency, the core is ideal for the implementation of TSN Ethernet nodes, live streaming and other devices requiring minimum latency in the reception and transition of Ethernet frames.

-

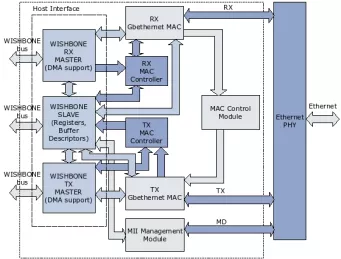

MAC 10/100/1000 Ethernet Controller

- IEEE 802.3-2002 specification with preamble, start-of-frame delimiter (SFD), frame padding generation and cyclic redundancy code (CRC) generation and checking is fully implemented

- Supports 10/100 Mbps or 1000 Mbps operation (selectable via a core configuration registers)

- Supports full- and half-duplex operation (selectable via a core configuration registers)

- CSMA/CD protocol for half-duplex operation

-

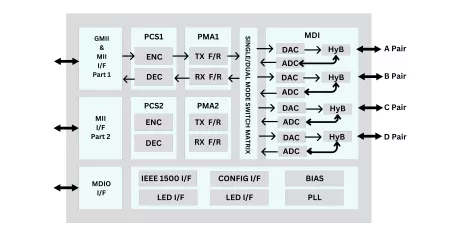

GbE (10/100/1000 Base-T) PHY IP, Silicon Proven in TSMC 28HPC+

- IEEE 802.3-2008, IEEE 802.3az fully standards compliant

- IEEE 1588-2008 support

- BroadR-Reach™ support

- Dual port MAC interface: GMII (10/100/1000BASE-T), MII (10/100BASE-T).

-

Silicon Proven 1G Ethernet PHY IP as Whitebox

- IEEE 802.3-2008, IEEE 802.3az fully standards compliant

- IEEE 1588-2008 support

- BroadR-Reach™ support

- Dual port MAC interface:

-

GbE (10/100/1000 Base-T) PHY IP, Silicon Proven in UMC 28HPC

- Fully compliant with the IEEE 802.3 / 802.3u/802.3ab10BASE-Te, 100BASE-TX ,1000BASE-T

- Interface available to Compliant with TP-PMD standard:ANSI X3.263-1995, Compliant with FDDIPMD standard: ISO/IEC 9314-3: 1990 and ANSIX3.166-1990

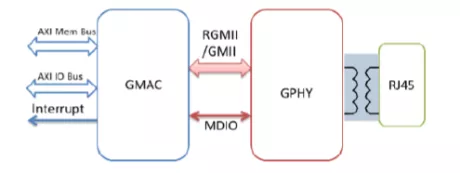

- Support GMII / RGMII interface to the MAC controller.?Serial management interface compliant with IEEE802.3u (MDIO)

- Support Full-Duplex or Half-Duplex Operation,1000BASE Full-Duplex only

-

10/100/1000 Mbps Ethernet MAC

- Designed according to IEEE 802.3-2005 Specification.

- Support 10/100/1000 Mbps Ethernet MAC Speed in Halfduplex and Full-duplex mode.

- Promiscuous receive mode support.

- Untagged frames support.