MIPI C-PHY/D-PHY Combo IP

Welcome to the ultimate MIPI C-PHY/D-PHY Combo IP hub! Explore our vast directory of MIPI C-PHY/D-PHY Combo IP

All offers in

MIPI C-PHY/D-PHY Combo IP

Filter

Compare

122

MIPI C-PHY/D-PHY Combo IP

from

13

vendors

(1

-

10)

-

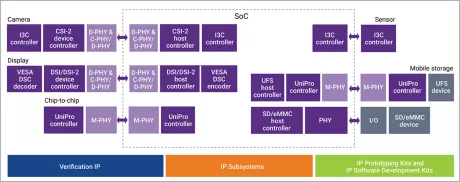

MIPI C/D-PHY Combo IP

- Compliant to MIPI D-PHY v3.0, C-PHY v2.1 specification

- Area efficient macro optimized for placement for dense SoC designs

- Support Uni-(TX or RX) and Bi-directional(TX and RX) mode

- Support emphasis architecture over lossy channel for TX

- Support equalize architecture over lossy channel for RX

-

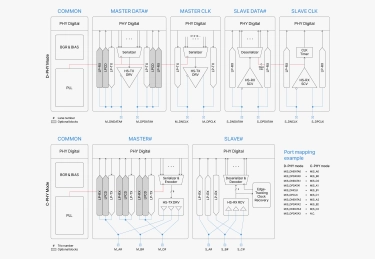

MIPI C-PHY℠ v2.0 + D-PHY℠ v2.5 Combo IP Core

- This Tx/Rx transceiver complies with the MIPI Alliance C-PHY℠ v2.0 and D-PHY℠ v2.5 specifications, with world-class area and power dissipation, and is available for a range of foundry processes.

- This IP delivers 6 Gbps per lane for a max throughput of 24 Gbps in D-PHY℠ mode, and 6 Gsps per trio for a max throughput of 41.04 Gbps in C-PHY℠ mode.

-

Combination MIPI CPHY-DPHY Analog Interface

- The MIPI C-PHY V1.2 improves throughput over a bandwidth-limited channel, allowing more data without an increased signaling clock.

- It is intended to be used for camera interface (CSI-2 v1.3) and display interface (DSI-2 v1.0).

- The signaling interface uses a 3-phase transceiver that encodes 3-bit symbols over 3 wires

-

MIPI C-PHY/D-PHY Combo IP

- The MIPI C/D-PHY combo IP is a high-frequency low-power, low cost, physical layer compliant with the MIPI® Alliance Standard for C-PHY and D-PHY.

- The PHY can be configured as a MIPI Master or MIPI Slave, supporting camera interface CSI-2 v1.2 or display interface DSI v1.3 applications in the D-PHY mode. It also supports camera interface CSI-2 v1.3 and display interface DSI-2 v1.0 applications in the C-PHY mode.

-

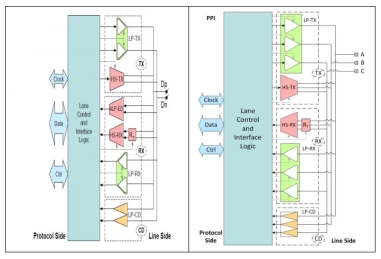

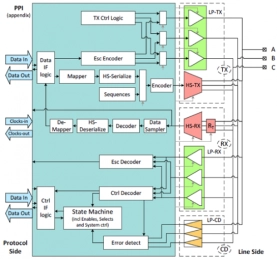

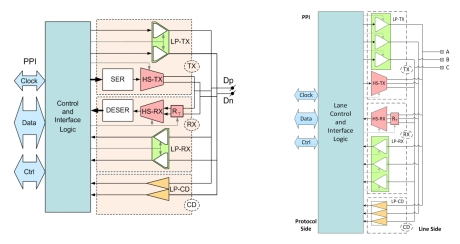

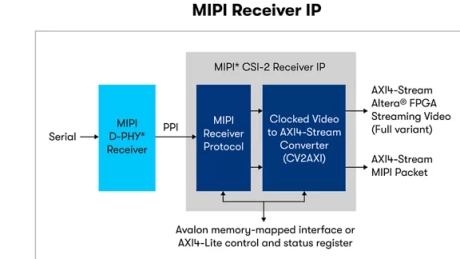

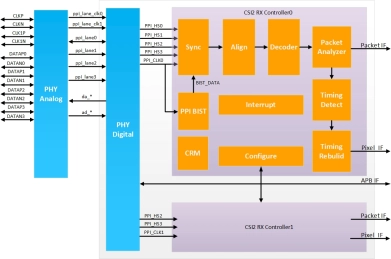

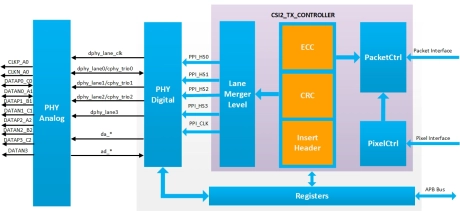

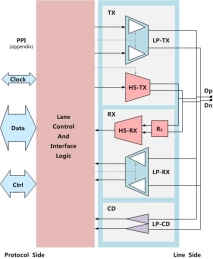

MIPI D-PHY IP

- Mobile Industry Processor Interface (MIPI) D-PHY is supported on Agilex™ 5 and Agilex™ 3 FPGAs allowing transmission and reception of data through PHY-protocol interface (PPI) to connect with camera serial interface (CSI) and display serial interface (DSI) applications.

-

MIPI D-PHY1.2 CSI/DSI TX and RX

- The MIPI D-PHY + DSI/CSI Controller IP is a versatile solution designed for high-speed data transmission in mobile and multimedia applications

- It supports MIPI D-PHY 2.0 standards

- The IP features a compact design with built-in I/O and ESD protection, optimized for robust performance and low power consumption

- It enables seamless connectivity with D-PHY based sensors, making it ideal for SoCs in consumer electronics, automotive, and IoT devices

-

MIPI C/D-PHY CSI/DSI TX and RX

- The MIPI C/D-PHY + DSI/CSI Controller IP is a versatile solution designed for high-speed data transmission in mobile and multimedia applications

- It integrates C-PHY and D-PHY in a single IP core, supporting both MIPI C-PHY 1.1 and D-PHY 2.0 standards

- The IP features a compact design with built-in I/O and ESD protection, optimized for robust performance and low power consumption

-

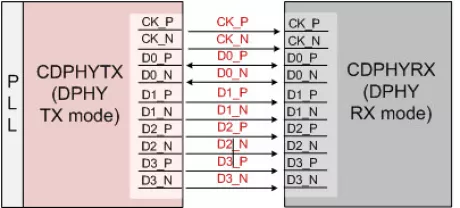

MIPI C/D PHY

- Compatible with MIPI D-PHY v1.2/CSI-2 protocol

- Up to 4-lane 2.5Gbps/ lane

- Support 2-Lane/4-Lane Application

- Support HS mode (80Mbps to 2.5Gbps per lane) and LP mode (up to 10Mbps)

-

MIPI C/D Combo PHY RX - GlobalFoundries 22FDX

- Supports up to one clock lane and four data lanes for DPHY1.2

- Fully compliant with MIPI D-PHY v1.2 and C-PHY v1.0 spec

- Available in GlobalFoundries 22FDX process

- Three 3phase encoded data lanes for CPHY1.0

-

MIPI C-PHY v1.2 D-PHY v2.1 RX 3 trios/4 Lanes - TSMC7FF 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v2.1

- 4 Lanes in D-PHY mode up to 6.5Gb/s per lane

- Compliant with the MIPI C-PHY specification, v2.0

- 3 trios in C-PHY mode up to 6.5Gs/s per trio