eFPGA IP for UMC

Welcome to the ultimate

eFPGA IP

for

UMC

hub! Explore our vast directory of

eFPGA IP

for

UMC

All offers in

eFPGA IP

for

UMC

Filter

Compare

1

eFPGA IP

for

UMC

from

1

vendors

(1

-

1)

-

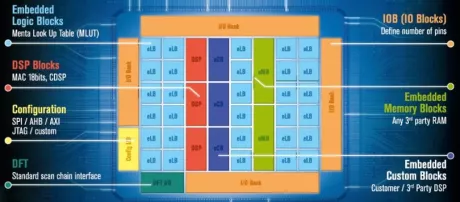

eFPGA Soft IP

- These eFPGA IP cores offer designers the flexibility to tailor resources to their application requirements, available as either Soft RTL or Hard GDSII IP.

- Our standard-cell-based approach facilitates rapid porting to new process geometries or variants, including industrial and rad-hard grade versions.