Clock Generator PLL IP for UMC

Welcome to the ultimate

Clock Generator PLL IP

for

UMC

hub! Explore our vast directory of

Clock Generator PLL IP

for

UMC

All offers in

Clock Generator PLL IP

for

UMC

Filter

Compare

93

Clock Generator PLL IP

for

UMC

from

2

vendors

(1

-

10)

-

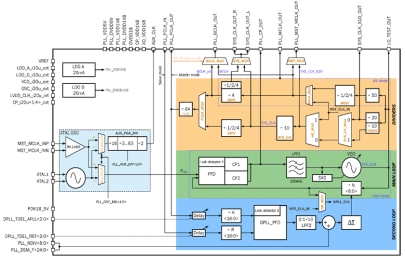

2.26GHz/2.46GHz Fractional-N LC Phase-Locked Loop with oscillator

- 180XFAB_PLL_01 uses 2.25792GHz/2.4576GHz Phase locked loop frequency synthesizer for clock generation.

- It consists of the following main sub-blocks: reference oscillator; main PLL loop: Fractional-N PLL and VCO blocks; secondary digital PLL loop: synchronization subsystem; dividers block: clock generation/delivery subsystem; voltage stabilizers.

- High frequency synthesis is needed for both phase noise performance and ultra-fine frequency tuning step.

-

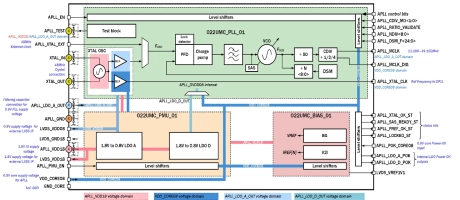

10MHz to 50MHz fractional-N PLL synthesizer

- UMC 22nm ULP technology

- 1.8V IO power supply

- Double 0.8/1.0V Core power supply

- Embedded low noise bias

-

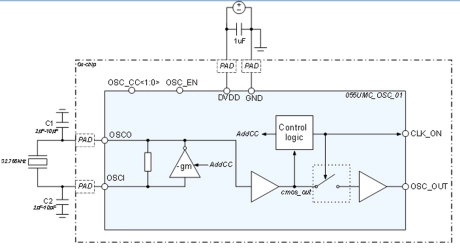

Ultra low power 32.768 kHz crystal oscillator

- UMC 55nm eFlash CMOS technology

- Input Voltage 1.2V

- Fixed 32.768kHz output frequency

-

UMC L90SP 90nm Clock Generator PLL - 120MHz-600MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

UMC L90SP 90nm Clock Generator PLL - 60MHz-300MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

UMC L90SP 90nm Clock Generator PLL - 240MHz-1200MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

UMC L90GOD 90nm Clock Generator PLL - 250MHz-1250MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

UMC L90GOD 90nm Clock Generator PLL - 125MHz-625MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

UMC L90GOD 90nm Clock Generator PLL - 500MHz-2500MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

UMC L90G 90nm Clock Generator PLL - 180MHz-900MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.