HBM IP for TSMC

Welcome to the ultimate

HBM IP

for

TSMC

hub! Explore our vast directory of

HBM IP

for

TSMC

All offers in

HBM IP

for

TSMC

Filter

Compare

6

HBM IP

for

TSMC

from

2

vendors

(1

-

6)

Filter:

- 3nm

-

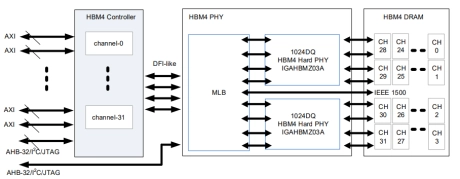

TSMC CLN3FFP HBM4 PHY

- IGAHBMZ03A is a High Bandwidth Memory 4 Physical Layer (HBM4 PHY) that is compliant with JEDEC HBM4 DRAM Specification JESD270-4.

- Fabricated in the TSMC 3 nm Advanced process node (N3P), it supports the data rate up to 12 Gbps per data pin in the DDR PHY Interface (DFI)-like 1:4 clock frequency ratio (HBM4 controller clock: WDQS = 1:4).

-

HBM3 PHY V2 (Hard) - TSMC N3P

- Supports 2.5D-based JEDEC standard HBM3 DRAMs with data rates up to 9600 Mbps

- 16 independent 64-bit memory channels

- Pseudo-channel operation supported to enable up to 32 32-bit pseudo-channels with 1024-bit PHY

- Supports up to 4 trained frequencies with <5us switching time

-

HBM3 PHY V2 - TSMC N3E

- Supports 2.5D-based JEDEC standard HBM3 DRAMs with data rates up to 9600 Mbps

- 16 independent 64-bit memory channels

- Pseudo-channel operation supported to enable up to 32 32-bit pseudo-channels with 1024-bit PHY

- Supports up to 4 trained frequencies with <5us switching time

-

HBM3 V2 Solution enabling access to HBM3 Controller and HBM3 PHY in TSMC N3E

- JEDEC HBM 3.0 DRAM

- DFI 5.0 compliant interface to HBM3 PHY

- Multiport Arm® AMBA® interface (4 AXI AXI™) with managed QoS or single-port host interface, per pseudo-channel

- Data rates up to 6.4 Gbps (DFI 1:1:2) (1.6GHz controller clock)

-

TSMC CLN16FFGL+ HBM PHY IP

- High Bandwidth Memory (HBM) DRAM PHY

- Supports HBM 2Gbps

- Supports DFI 1:2

- Supports only BL4