USB 3.0 IP for TSMC

Welcome to the ultimate

USB 3.0 IP

for

TSMC

hub! Explore our vast directory of

USB 3.0 IP

for

TSMC

All offers in

USB 3.0 IP

for

TSMC

Filter

Compare

5

USB 3.0 IP

for

TSMC

from

3

vendors

(1

-

5)

Filter:

- 28nm

-

USB 3.0 PHY

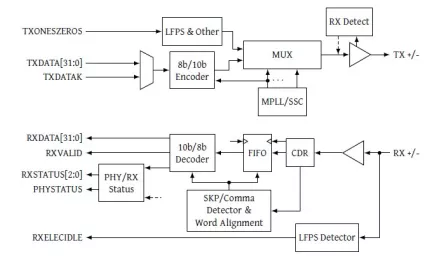

- Standard PHY interface (PIPE) enables multiple IP sources for USB 3.0 Link Layer

- Supports 5.0 GT=s serial data transmission rate

- Supports 16- or 32-bit parallel interface

- Supports PCLK as PHY output

-

USB 3.1 PHY

- Parallel data widths of 8bits and 16bits

- QUAD configuration (4TX and 4RX), Single lane configuration (1TX and 1RX)

- Support signal loss and receiver detection using programmable multi-tap & de-emphasis

- Support 1m cable

-

USB 3.0 PHY in TSMC (65nm, 55nm, 40nm, 28nm)

- Complete mixed-signal physical layer for USB 3.0 applications

- Includes all circuitry needed for operation at all USB speeds (SuperSpeed, High-Speed, FullSpeed, Low-Speed)

- USB-C 3.0 femtoPHY supports Type-C reversible connectors

- Optimized PHY area (<0.5mm2 for USB 3.0, <0.8mm2 for USB-C 3.0)

-

USB-C 3.0 femtoPHY in Type-C in TSMC (28nm, 16nm, 12nm)

- Complete mixed-signal physical layer for USB 3.0 applications

- Includes all circuitry needed for operation at all USB speeds (SuperSpeed, High-Speed, FullSpeed, Low-Speed)

- USB-C 3.0 femtoPHY supports Type-C reversible connectors

- Optimized PHY area (<0.5mm2 for USB 3.0, <0.8mm2 for USB-C 3.0)

-

USB 3.0 femtoPHY in TSMC (28nm, 22nm, 16nm, 12nm)

- Complete mixed-signal physical layer for USB 3.0 applications

- Includes all circuitry needed for operation at all USB speeds (SuperSpeed, High-Speed, FullSpeed, Low-Speed)

- USB-C 3.0 femtoPHY supports Type-C reversible connectors

- Optimized PHY area (<0.5mm2 for USB 3.0, <0.8mm2 for USB-C 3.0)