USB IP for TSMC

Welcome to the ultimate

USB IP

for

TSMC

hub! Explore our vast directory of

USB IP

for

TSMC

All offers in

USB IP

for

TSMC

Filter

Compare

17

USB IP

for

TSMC

from

3

vendors

(1

-

10)

Filter:

- 7nm

-

USB4 PHY - TSMC N7 1.8V, North/South Poly Orientation

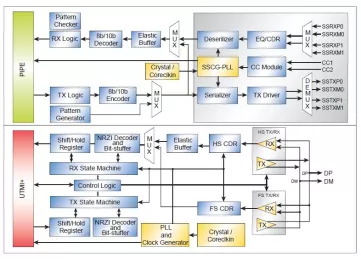

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

-

USB 2.0 PHY

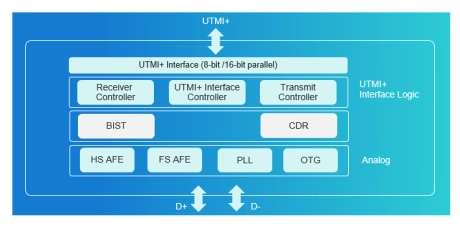

- Designed to the USB 2.0 specification, and operates at High Speed (480Mbps), Full Speed (12Mbps), and Low Speed (1.5Mbps)

- Complies with the UTMI v1.05 specification

- Multiple reference clock supported from 9.6MHz up to 52MHz

- 8-bit 60MHz and 16-bit 30MHz parallel interfaces

- Battery Charging Specification v1.2

-

USB 2.0 femtoPHY - TSMC 7FF18 x1, OTG, North/South (vertical) poly orientation

- Ported to over 50 different processes and configurations ranging from 65-nm to 14/16-nm FinFET

- Supports the USB 2.0 protocol and data rate (480 Mbps)

- Supports the USB Type-C specification

- USB femtoPHY, USB nanoPHY and USB picoPHY offer a tunability feature that allows quick, post-silicon adjustments that occur due to process variations, or unexpected chip and board parasitic, without modifying the existing design

-

USB-C 3.1/DP TX PHY for TSMC N7, North/South Poly Orientation for Automotive AEC-Q100 Grade 2

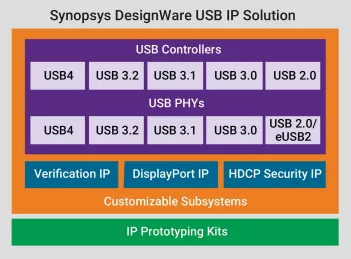

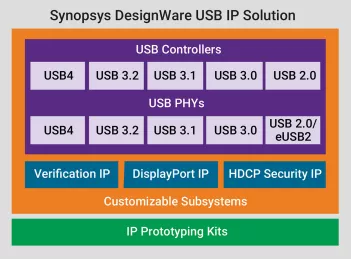

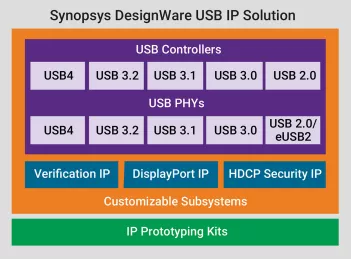

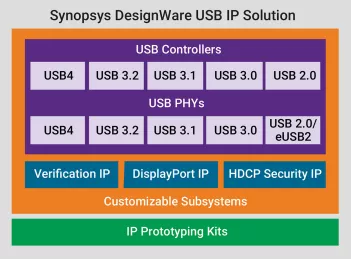

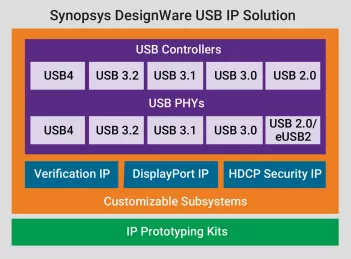

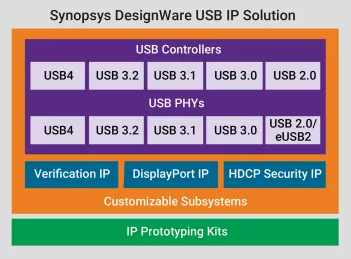

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB-C 3.1 SS/SSP PHY, Type-C - TSMC 7FF x1, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB-C 3.1/DP TX PHY for TSMC 7FF, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB 3.1 PHY (10G/5G) - TSMC 7FF x1 OTG, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

eUSB2 v1.1 Dual-Role, repeater/native mode PHY, TSMC N7, 1.8V or 1.2V, N/S orientation

- Fully compliant with Embedded Universal Serial Bus 2.0 (eUSB) electrical specification

- Compliant with UTMI+ specifications (High-speed, Full-speed, and Low-speed functions)

- Support clock inputs from 10/12/25/30/19.2/24/32/38.4MHz clock source

- Support repeater and native modes

-

USB4 Gen3 x2-lane PHY, TSMC N7, 1.8V or 1.2V, N/S orientation, type-C

- Compliant to USB4 Gen3(20G) / Gen2(10G)

- Support USB4 Gen3 PIPE SerDes (128b/132b) coding

- Support USB4 Gen2 PIPE SerDes (64b/66b) coding

- Support PIPE USB3.2 Gen2 (128b/132b) coding

-

USB-C 3.1 SS/SSP PHY in Type-C in TSMC (16nm, 12nm, N7, N6, N5, N5A)

- Lowest risk: Based on proven USB 3.0 controller shipped in 100s of millions of units

- Lowest power: Extend battery life in mobile devices (USB power saving modes, Uniform Power Format, hibernation option with dual power rails)

- Configurable data buffering options to optimize performance vs area

- Supports all USB speed modes