Ethernet PHY IP for TSMC

Welcome to the ultimate

Ethernet PHY IP

for

TSMC

hub! Explore our vast directory of

Ethernet PHY IP

for

TSMC

All offers in

Ethernet PHY IP

for

TSMC

Filter

Compare

20

Ethernet PHY IP

for

TSMC

from

4

vendors

(1

-

10)

-

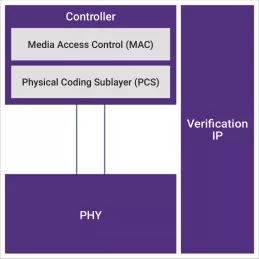

Ultra-Low-Latency 10GE PHY+MAC

- Ultra-low-latency round-trip (fiber-to-fiber or gate-to-gate) for 10 Gigabit Ethernet, first-bit to first-bit

- Reconciliation sub-layer implementation compliant with IEEE802.3

- Local fault and remote fault detection and handling

- Frame Check Sequence (FCS) insertion and verification at line rate

-

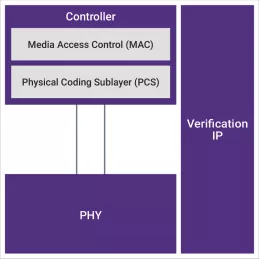

224G Ethernet PHY, TSMC N3P x1, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications

-

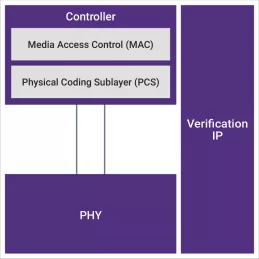

224G Ethernet PHY, TSMC N3E x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications

-

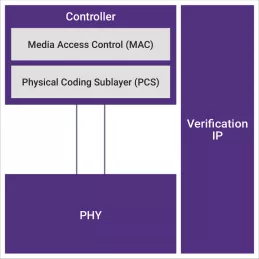

112G PHY, TSMC N7 x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N7 x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N7 x2, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N7 x1, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N6 x2, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N6 x1, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N5 x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects