PLL IP for TSMC

Welcome to the ultimate

PLL IP

for

TSMC

hub! Explore our vast directory of

PLL IP

for

TSMC

All offers in

PLL IP

for

TSMC

Filter

Compare

837

PLL IP

for

TSMC

from

24

vendors

(1

-

10)

-

1.7GHz Multiplying PLL on TSMC 28nm

- Including Loop-filter

- VCO operating range : 850MHz - 1700 MHz

- Output frequency range : 850MHz -1700 MHz

- Input frequency range : 9.6MHz - 216MHz

-

5GHz Multiplying PLL on TSMC 28nm

- Including Loop-filter

- VCO operating range : 2500MHz - 5000 MHz

- Output frequency range : 1250MHz - 2500 MHz

- Input frequency range : 12MHz - 320 MHz

-

1.8GHz SSCG PLL on TSMC 28nm HPC+

- Including Loop-filter

- VCO operating range : 900MHz - 1800 MHz

- Output frequency range : 900MHz-1800 MHz

- Input frequency range : 12MHz - 192MHz

-

3.2GHz SSCG PLL on TSMC 12nm

- Including Loop filter

- VCO operating range : 1600MHz- 3200MHz

- Output frequency range: 400MHz- 3200MHz

- Input frequency range : 10MHz- 200MHz

-

4.3GHz SSCG PLL on TSMC 7nm

- Including Loop filter

- VCO operating range : 2000MHz-4300MHz

- Output frequency range: 500MHz-4300MHz

- Input frequency range : 10MHz- 200MHz

-

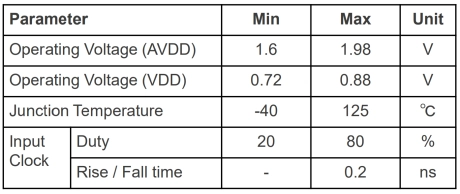

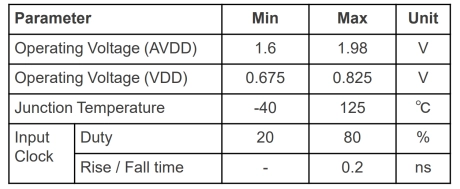

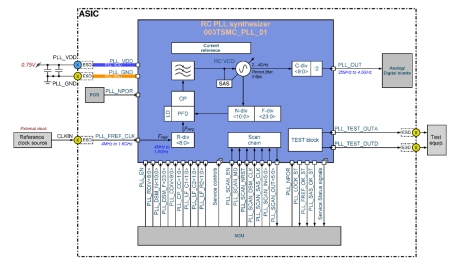

25MHz to 4.0GHz Fractional-N RC PLL Synthesizer on TSMC 3nm N3P

- Fractional-N Phase locked loop frequency synthesizer is intended for ASIC clock generation.

- The Fractional-N PLL loop with 2GHz-4GHz VCO has high phase noise performance and ultra-fine frequency tuning step.

- VCO Sub-band auto select (SAS) system allows to find automatically appropriate sub-band for VCO on locked PLL.

-

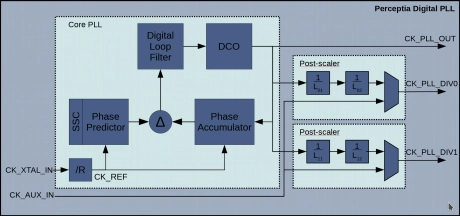

All Digital Fractional-N RF Frequency Synthesizer PLL in TSMC N6/N7

- Fractional Multiplication with frequencies up to 8GHz

- Extremely low jitter (sub 300fs RMS)

- Small size (< 0.05 sq mm)

- Low Power (< 7mW)

-

All Digital Fractional-N PLL for Performance Computing in TSMC N6/N7

- Fractional multiplication with frequency up to 4GHz

- Low jitter (< 10ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 5mW)

- Support for multi-PLL systems

-

Low Power All Digital Fractional-N PLL in TSMC N6/N7

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

Low Power All Digital Fractional-N PLL in Samsung 8LPP

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz