Voltage Regulator IP for SMIC

Welcome to the ultimate

Voltage Regulator IP

for

SMIC

hub! Explore our vast directory of

Voltage Regulator IP

for

SMIC

All offers in

Voltage Regulator IP

for

SMIC

Filter

Compare

53

Voltage Regulator IP

for

SMIC

from

10

vendors

(1

-

10)

-

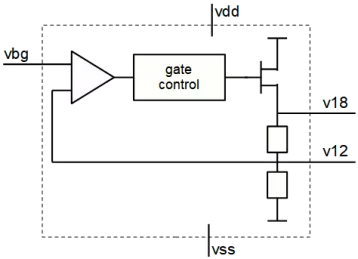

75mA Core Voltage Regulator

- Input voltage range 3.0V – 3.3V.

- Output voltage 1.2V or 1.8V ±4%.

- Output short circuit protection.

- Bundled with Obsidian 1.2V bandgap reference.

- Power down/enable input.

- Fast response to current steps.

-

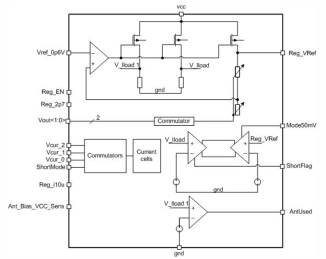

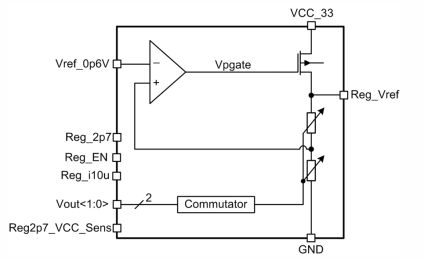

LDO voltage regulator (output voltage value 1.8 V, 2.4 V, 2.7 V, 3.0 V)

- SMIC CMOS 0.18 um

- High precision stabilization voltage

- Several operating modes

- Differential output voltage value (1.8 V, 2.4 V, 2.7 V, 3.0 V)

-

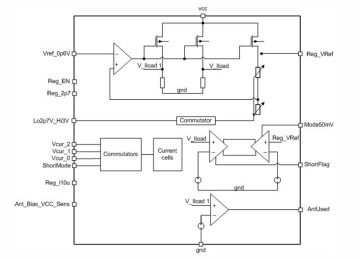

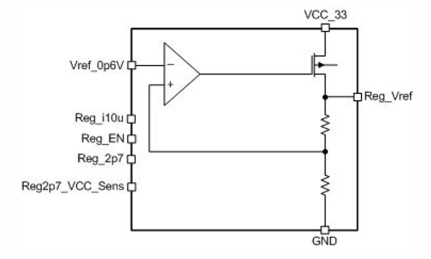

LDO voltage regulator (output voltage value 2.7 V, 3.0 V)

- SMIC CMOS 0.18 um technology

- High precision stabilization voltage

- Several operating modes

- Different output voltage value (2.7 V, 3.0 V)

-

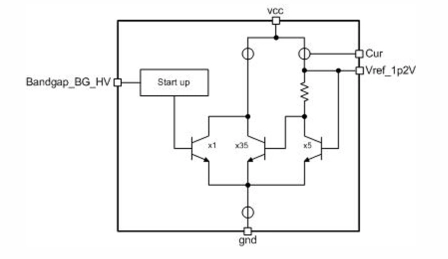

1.2 V Bandgap voltage reference

- SMIC CMOS 0.18 um

- Output voltage 1.2 V

- Temperature-compensated voltage in a wide temperature range

- Low current consumption

-

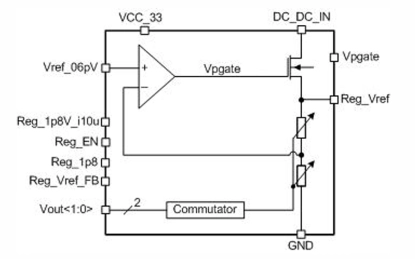

LDO voltage regulator (output voltage value 1.8 V, 2.1 V, 2.4 V, 2.7 V)

- SMIC CMOS 0.18 um

- High precision stabilization voltage

- Several operating modes

- Different output voltage value (1.8 V, 2.1 V, 2.4 V, 2.7 V)

-

LDO voltage regulator (output voltage 2.7 V)

- SMIC CMOS 0.18 um

- Output voltage 2.7 V

- High precision stabilization voltage

- Several operating modes

-

LDO voltage regulator (output voltage value 1.0 V, 1.2 V, 1.5 V, 1.8 V)

- SMIC CMOS 0.18 um

- High precision stabilization voltage

- Different output voltage value (1.0 V, 1.2 V, 1.5 V, 1.8 V)

- Several operating modes

-

Ultra low power LDO

- 500mA maximum output current

- Ultra low quiescent current

- low dropout voltage

- Current limit protection

- OTP/OVP/UVP/PGOOD

-

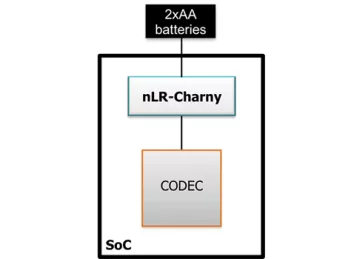

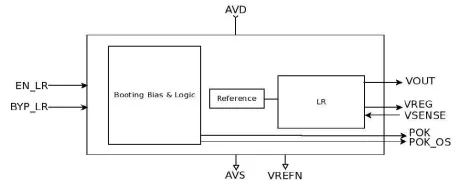

Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference

- Starring a PSRR of -65 dB at 20 kHz and a low intrinsic noise, combined with a low quiescent current of 110 uA, the nLR-VAIPO helps optimize the power management network for audio handheld applications such as smartphone and tablet.

- Small footprint: only 0.12 mm2 (including bandgap reference and POK circuit)

- Minimization of the overall system power, through the support of 3 modes of operation: normal, shutdown and bypass

- Eases integration in SoC nLR-VAIPO is delivered with behavioral models. These new views enable to build an optimized Power Management Network (PMNet) by verifying mode transitions as well as noise propagation.

-

Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks

- Low noise: high power Supply Rejection Ratio (PSRR): - 65 dB at F < 10 kHz

- Low intrinsic noise: 20 uVRMS at 10 Hz to 20 kHz

- Low Bill-of-Material: optimized in density for the best trade-off for the given output current and input voltage range

- Cost efficient solution compared to external Power Management.