DDR5 IP for Samsung

Welcome to the ultimate

DDR5 IP

for

Samsung

hub! Explore our vast directory of

DDR5 IP

for

Samsung

All offers in

DDR5 IP

for

Samsung

Filter

Compare

13

DDR5 IP

for

Samsung

from

2

vendors

(1

-

10)

-

DDR5/4 PHY V2C CU - SS SF4X

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

DDR5 PHY - SS SF4X

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

DDR5/4 PHY V2 - SS 8LPU

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

DDR5/4 PHY - SS 7LPP

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

DDR5/4 PHY - SS 10LPP

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

DDR5/4 PHY for Samsung

- Lowest latency for data-intensive applications

- Highest data rates with detailed system guidelines

-

DDR5 PHY in Samsung (SF4X)

- Low latency, small area, low power

- Compatible with JEDEC standard DDR5 SDRAMs up to 8400 Mbps

- Compatible with JEDEC standard DDR4 SDRAMs up to 3200 Mbps

- DFI 5.0 compliant interface to the memory controller

-

DDR4 multiPHY in Samsung (14nm)

- Low latency, small area, low power

- Compatible with JEDEC standard DDR4 up to 2667 Mbps

- Compatible with JEDEC standard DDR3 SDRAMs up to 2133 Mbps

- Compatible with JEDEC standard LPDDR2 SDRAMs up to 1066 Mbps

-

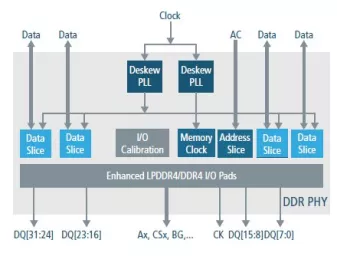

LPDDR4X multiPHY in Samsung (14nm, 11nm)

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

LPDDR4 multiPHY V2 in Samsung (8nm) for Automotive

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps