Memory Controller/PHY IP for GLOBALFOUNDRIES

Welcome to the ultimate

Memory Controller/PHY IP

for

GLOBALFOUNDRIES

hub! Explore our vast directory of

Memory Controller/PHY IP

for

GLOBALFOUNDRIES

All offers in

Memory Controller/PHY IP

for

GLOBALFOUNDRIES

Filter

Compare

12

Memory Controller/PHY IP

for

GLOBALFOUNDRIES

from

3

vendors

(1

-

10)

Filter:

- 12nm

-

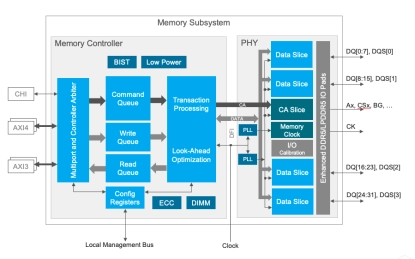

DDR PHY

- DDR5/4/3 training with write-leveling and data-eye training

- Optional clock gating available for low-power control

- Internal and external datapath loop-back modes

- I/O pads with impedance calibration logic and data retention capability

- Programmable per-bit (PVT compensated) deskew on read and write datapaths

- RX and TX equalization for heavily loaded systems

-

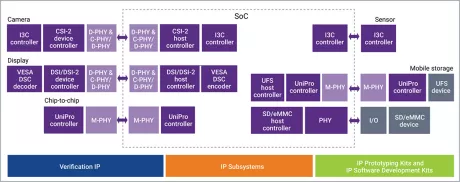

SD/eMMC - GlobalFoundries 12LP, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

LPDDR5/4/4X PHY - GF 12LP+ for Automotive ASIL B Random, AEC-Q100 Grade 1

- Supports JEDEC standard LPDDR5X, LPDDR5, LPDDR4 and LPDDR4X SDRAMs

- Support for data rates up to 6400 Mbps

- Designed for rapid integration with Synopsys’ LPDDR5/4/4X controller for a complete DDR interface solution

- DFI 5.0 controller interface

-

LPDDR5/4/4X PHY - GF 12LP+

- Supports JEDEC standard LPDDR5X, LPDDR5, LPDDR4 and LPDDR4X SDRAMs

- Support for data rates up to 6400 Mbps

- Designed for rapid integration with Synopsys’ LPDDR5/4/4X controller for a complete DDR interface solution

- DFI 5.0 controller interface

-

DDR5/4 PHY - GF 12LP+

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

GDDR6 PHY IP on GF 12nm LPP

- The UniIC GDDR6 PHY,subsequently referred to as the UNIIC_GD6PHY, is designed for performance and power efficiency, its target is to deliver industry-leading data rates of up to 12Gbps/13Gbps/14Gbps and is compatible with JEDEC standard JEDEC250 and DFI 3.1

- The UNIIC_GD6PHY is used to transfer the Command/Address and Datas between the memory controller and the GDDR6 DRAM device; _x000D_ The UNIIC_GD6PHY is available in Global Foundries FinFET 12LPP technology

- The UNIIC_GD6PHY is fully documented and comes with a comprehensive set of deliverables for ease of system modeling and integration.

-

DDR4 Multi-modal PHY - GLOBALFOUNDRIES 12nm

- PLL-based clocking with internal clock alignment to the parallel clock on the memory controller interface

- Autonomous initialization

- Support for x72 bit channel

- Support for multiple DRAM widths (x4, x8, x16, x32)

-

DDR4 PHY - GLOBALFOUNDRIES 12nm

- PLL-based clocking with internal clock alignment to the parallel clock on the memory controller interface

- Autonomous initialization

- Support for x72 bit channel

- Support for multiple DRAM widths (x4, x8, x16, x32)

-

LPDDR4X multiPHY Plus in GF (12nm)

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

DDR5/4 PHY in GF (12nm)

- Low latency, small area, low power

- Compatible with JEDEC standard DDR5 SDRAMs up to 8400 Mbps

- Compatible with JEDEC standard DDR4 SDRAMs up to 3200 Mbps

- DFI 5.0 compliant interface to the memory controller