Synopsys Delivers First Complete UFS 5.0 and M‑PHY v6.0 IP Solution for Next‑Gen Storage

Introduction

As data volumes grow across mobile, automotive, and AI-enabled systems, storage performance has become a critical factor in overall SoC capability. Faster compute and richer software place increasing pressure on storage subsystems to deliver higher bandwidth, lower latency, and greater efficiency—without adding complexity or risk to designs.

To address these challenges, Synopsys is announcing the industry’s first complete IP solution for UFS 5.0, UniPro 3.0, and M‑PHY v6.0—bringing together the protocol, link, and physical layers required to enable the next generation of high‑speed, low power, high‑efficiency storage. Synopsys has also successfully completed silicon bring‑up of M‑PHY v6.0 on TSMC’s advanced N2P node, validating Gear6B operation with PAM‑4 signaling at 23.3 GBaud/s (46.7 Gbits/s) per lane. This milestone confirms readiness of the physical layer for UFS 5.0 adoption, giving customers confidence to design for the next wave of data‑intensive applications.

Storage Performance Is Now a System-Level Constraint

In many SoCs today, storage bandwidth no longer keeps pace with advances in compute and memory:

- AI workloads depend on rapid access to models and data.

- Camera, graphics, and media pipelines generate higher sustained throughput requirements.

- Software stacks continue to grow in size and complexity, increasing pressure on storage responsiveness.

At the same time, designers face strict constraints:

- Tight power and thermal budgets

- Aggressive form-factor and area targets

- Accelerated product schedules

- Limited tolerance for risk

These competing demands make it difficult to scale storage performance using legacy interfaces. Simply increasing interface width or frequency often leads to higher power consumption, greater design complexity, or longer bring-up cycles.

UFS 5.0, together with M-PHY v6.0 and UniPro 3.0, address these challenges by scaling bandwidth in a more efficient and system-friendly way.

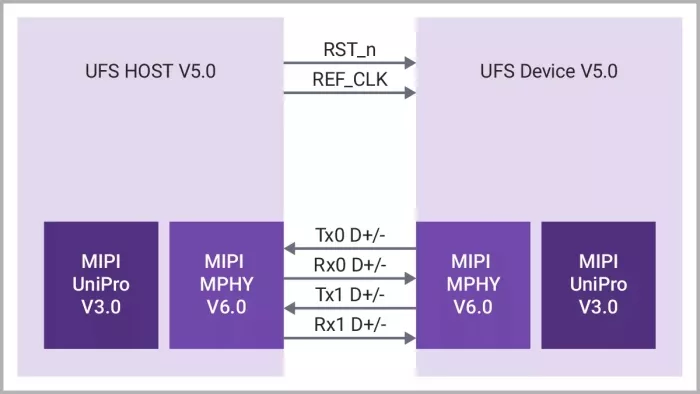

The Technology Underneath: UniPro 3.0 and M‑PHY v6.0 as the Backbone of UFS 5.0

UFS 5.0 is fundamentally built on the M-PHY and UniPro layers, which together form the physical, link, and transport foundation of the standard. UFS 5.0 requires both UniPro 3.0 and MPHY v6.0, and the new Synopsys UFS 5.0 IP solution integrates these 3-layers for next generation storage devices. MPHY v6.0 provides the highspeed physical interface, enabling significantly higher per lane data rates through PAM4 signaling and supporting the bandwidth needed for UFS 5.0 without increasing interface width or system complexity.

Most of the software interface remains unchanged. The use of the higher Gear 6 (G6) data rate follows the same Power Mode Change mechanism as earlier versions. However, for link training, UFS 5.0 introduces a dedicated equalization procedure, which is used to ensure signal quality and reliable operation at these higher data rates.

On top of the PHY, UniPro 3.0 adds the updated link and transport layer capabilities required to efficiently move data at these higher speeds, including lower overhead with 1b1b encoding and streamlined communication across the entire pipeline.

By integrating UFS 5.0, UniPro 3.0, and MPHY v6.0 into a single complete IP solution, Synopsys ensures customers can adopt next generation storage with confidence—supported by a cohesive and fully validated three-layer stack designed for maximum performance, scalability, and efficiency.

M-PHY v6.0 Silicon Bring-Up Enables Confident UFS 5.0 Adoption

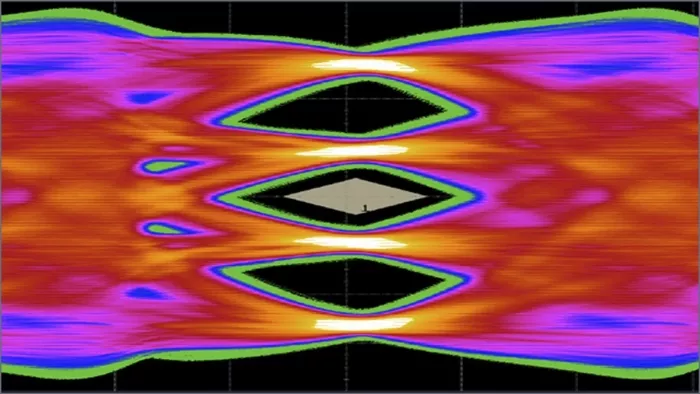

Synopsys recently completed silicon bring-up of M-PHY v6.0, demonstrating Gear6B operation with PAM-4 signaling at 23.3 GBaud/s (46.7 Gbits/s) per lane.

With the M-PHY v6.0 physical layer validated in silicon, development teams can move forward with greater confidence, reducing uncertainty around performance and integration at advanced speeds. This milestone provides assurance for customers planning UFS 5.0 designs.

Enabling High Performance Without Compromising Efficiency

One of the key advantages of the UFS 5.0 and M-PHY v6.0 combination is efficiency at scale. Higher per-lane bandwidth enables designers to meet growing storage performance requirements while keeping interface counts, routing complexity, and power consumption under control.

Applications include:

- Smart Phones: Faster storage with small form factor improves user experience while preserving battery life.

- Laptop PC Storage: High‑speed, low‑power storage option positioned as an SSD/NVMe alternative.

- Automotive Systems: High-speed storage supports infotainment, data logging, and ADAS within thermal limits.

- Edge AI Platforms: Rapid data access must coexist with constrained power envelopes.

- Gaming Consoles: Gaming platforms is shifting from removeable cards to embedded storage, which requires high-speed, low-power solution to deliver enhanced user experience.

Building on Interface IP Momentum Across TSMC N2 and N2P Nodes

The M-PHY v6.0 milestone builds on Synopsys’ broader momentum on TSMC N2 and N2P nodes. The industry-leading portfolio now includes:

- MIPI M-PHY IP

- MIPI C-PHY and D-PHY IP

- LPDDR6 IP

- USB IP

Together, this growing portfolio enables customers to pursue ambitious power, performance, and area targets with trusted interface solutions.

Positioning Designs for What Comes Next

As data driven workloads expand, storage bandwidth will remain a foundational enabler of system performance. With the new UFS 5.0 IP, UniPro 3.0 support, and M PHY Gear 6 IP, Synopsys is enabling customers to prepare for the next generation of high speed storage designs.

Related Semiconductor IP

- UFS 5.0 Host Controller IP

- Verification IP for UFS

- UFS Hardware Validation Platform (HVP)

- UFS 4.0 Host

- UFS 3.1 host

Related Blogs

- XConn Revitalizes Next-Gen Data Centers with CXL 2.0 Switch Designed with Synopsys IP

- Meeting the World's Growing Bandwidth Demands with a Complete 1.6T Ethernet IP Solution

- Industry's First Verification IP for Arm AMBA CHI-G

- Verifying CXL 3.1 Designs with Synopsys Verification IP

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk