Skymizer Reduces Verification Cycles for AI Accelerator IP Development by 33% with Synopsys HAPS Prototyping

With artificial intelligence (AI) being used for a growing number of use cases in an expanding set of industries, semiconductor providers face immense pressure to keep pace with rising workload complexity and specialization. From real-time language processing to vision-based applications and instruction-driven models, AI workloads require silicon solutions that are not only powerful but also efficient, optimized for specific use cases, and able to scale with the extension of AI infrastructure.

Those creating semiconductor IP for AI systems — like Skymizer, a Taipei-based developer of AI acceleration and compiler technology — must consider these requirements as early as possible. They must also foster interaction between IP providers, silicon integrators, and AI software developers for more seamless integration and optimized outcomes.

Leveraging the LISA v3 instruction set architecture (ISA), Skymizer envisioned meeting the rigorous demands of modern AI applications. Their plans included development of AI accelerator IP, called HyperThought, supporting multimodal and agentic AI. Skymizer’s design objective included enablement of real-time processing of language, vision, and instruction-based models within a compact, scalable subsystem. Skymizer envisioned a modular design that would allow seamless integration into a wide range of applications, from edge devices to complex automotive systems.

For verification and IP interface validation, as well as early interaction with their design partners and customers, Skymizer needed robust FPGA-based prototyping. They chose Synopsys HAPS technology based on the AMD VP1902 Adaptive SoC.

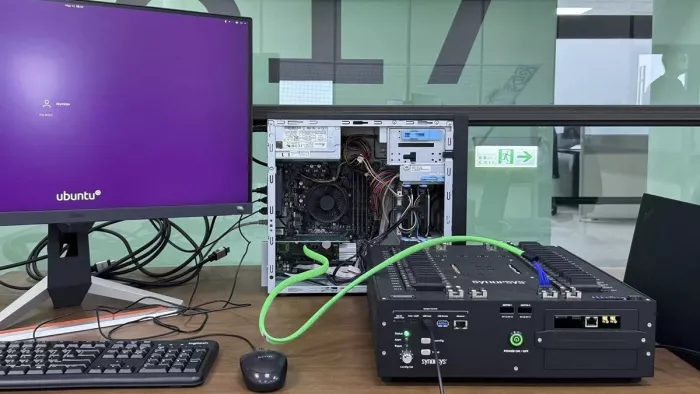

Figure 1: Skymizer used Synopsys’ VP1902-based HAPS technology to verify and demonstrate its HyperThought AI accelerator IP, utilizing HAPS’ high-performance execution and hardware/software co-development capabilities.

The need for speed in AI IP development

To meet their aggressive time-to-market goals for HyperThought, Skymizer needed an advanced prototyping platform that could handle the requirements of modern AI IP development. Based on the latest AMD VP1902 Adaptive SoC, HAPS provided the ideal solution.

By supporting pre-silicon system validation, hardware/software co-development, and “at-speed” prototyping, HAPS enabled Skymizer to streamline its development process and helped ensure that HyperThought met performance, interoperability, and reliability benchmarks early in the design cycle.

Key benefits of Synopsys’ VP1902-based HAPS technology include:

- Capacity: Execution of the entire Skymizer LPU design in a single FPGA without partitioning, using asynchronous clocking for high-performance prototyping.

- Performance: HAPS’ high runtime performance — tuned by Skymizer’s and Synopsys’ teams — for acceleration of verification cycles and faster time-to-market.

“With HAPS, our customers can experience HyperThought’s agentic AI and multimodal capabilities on real hardware, long before silicon is available,” says William Wei, CMO at Skymizer. “Our collaboration with Synopsys, showcasing prototypes of our LPU on accurate, fast hardware, allows us to interact with partners and customers in our ecosystem at the earliest point possible during the development cycle.”

How HAPS accelerates HyperThought development

Skymizer’s adoption of HAPS confirms the value of using HAPS for IP design verification, validation, and system development. By prototyping HyperThought on HAPS, Skymizer achieves:

- Hardware-verified innovation: Skymizer rapidly validated HyperThought IP on HAPS, ensuring it met target performance and reliability requirements. This pre-silicon validation stage reduces the risk of costly design iterations in silicon, accelerates the overall development timeline, and allows demonstration of its IP to customers.

- Unified hardware/software development: The robust debug and hybrid prototyping capabilities of HAPS allow Skymizer to bring up drivers, firmware, and applications in a hardware prototyping environment. This unified approach to hardware and software development minimizes risks and ensures a smoother transition to production.

- Accelerated time to prototyping model: Using HAPS ProtoCompiler, Skymizer automates critical tasks such as partitioning, timing, and connectivity. This enables the team to implement and debug HyperThought’s advanced features at real-world speeds, allowing for sufficient validation cycles.

- Scalability: HyperThought’s modular design combined with HAPS’ scalability to billion-gate capacity will enable scaling from edge devices to more complex systems. This flexibility allows HyperThought to meet the diverse needs of Skymizer’s customers.

Validating multimodal AI workflows at speed

One of the most compelling aspects of deploying HyperThought on HAPS is the ability to provide real-world validation of its capabilities. Skymizer’s IP development teams are able to validate multimodal AI workflows at speed, using HAPS hardware for system-level performance tuning. This approach not only helps ensure robust, production-ready IP — it also streamlines adoption of HyperThought customers and enables ecosystem collaboration for early software development.

In addition, Skymizer leverages Synopsys’ Verdi platform to debug across RTL and software layers. This comprehensive debugging capability allows the team to identify and resolve issues quickly, ensuring HyperThought can be ready for deployment in a wide range of applications.

Finally, IP Prototyping Kits based on HAPS have already enabled Skymizer’s partners and customers to evaluate and integrate HyperThought using PCIe interfaces. This streamlined approach to IP adoption enables greater collaboration across the ecosystem, accelerating the development of intelligent silicon solutions.

A bright future for AI IP and FPGA-based prototyping

Skymizer’s adoption of Synopsys HAPS technology is a great example of leading-edge development techniques for the development of AI accelerator IP. By leveraging HAPS prototyping capabilities, Skymizer was able to develop and validate HyperThought AI accelerator IP at a pace meeting today’s AI development needs.

As AI continues to drive demand for advanced silicon solutions, FPGA-based prototyping will be critical. Prototyping environments like HAPS enable development, verification, and demonstration of IP like HyperThought, widening the possibilities for intelligent, scalable, and efficient silicon to system designs. They empower SoC developers to turn ambitious ideas into reality — faster than ever.

Related Semiconductor IP

- LLM Accelerator IP for Multimodal, Agentic Intelligence

- NPU

- NPU IP Core for Edge

- NPU IP Core for Mobile

- NPU IP Core for Data Center

Related Blogs

- Trillions of Cycles per Day: How SiFive Boosts IP and Software Validation with Synopsys HAPS Prototyping System

- Faster, Higher Capacity Emulation and Prototyping for AI Workloads

- Do we need a new FPGA structure for prototyping?

- Virtual Platforms plus FPGA Prototyping, the Perfect Mix

Latest Blogs

- A Bench-to-In-Field Telemetry Platform for Datacenter Power Management

- IDS-Verify™: From Specification to Sign-Off – Automated CSR, Hardware Software Interface and CPU-Peripheral Interface Verification

- RISC-V and GPU Synergy in Practice: A Path Towards High-Performance SoCs from SpacemiT K3

- EDA AI Agents: Intelligent Automation in Semiconductor & PCB Design

- Why Security Can't Exist Without Trust