Semidynamics与SignatureIP 携手打造经过全面测试的RISC-V多核环境和CHI 互连方案

Advanced multi-core RISC-V chips can now easily be created for applications such as AI and ML

Barcelona, Spain – 3 October, 2023 -- There is an ever-increasing demand for more powerful chip designs for advanced applications, such as AI and ML, that require many cores on one chip. To facilitate this, Semidynamics and SignatureIP have partnered to integrate their respective IPs to provide a fully-tested RISC-V, multi-core environment and CHI interconnect for the development of state-of-the-art chip designs.

Semidynamics’ CEO and founder, Roger Espasa, said, “Working closely together with other members of the RISC-V community is one of the driving forces of RISC-V’s rapidly growing success. There is a natural synergy between the two companies that has resulted in a solution that enables cutting edge, multi-cores chips to be created. SignatureIP’s C-NoC CHI interconnect solution makes it very straightforward to lay out the Network on Chip (NoC) for multiple cores on a chip using our mature, proven technologies which minimizes risks and accelerates time to market.”

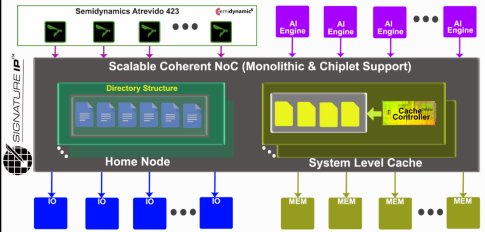

SignatureIP’s Coherent NoC is architected for performance and scalability across chiplets. It supports a transport layer for chiplet communication. The C-NoC IP is a directory-based architecture with distributed home-node support and optional system level caches for high performance. SignatureIP’s state-of-the-art inoculator.ai tool supports automation to generate a physically-aware NoC for a system. Combined with the automation tool and a simple licensing model, the process of evaluation, licensing, and implementation becomes an easy task for SignatureIP’s customers.

Kishore Mishra, SignatureIP’s CTO, added, “Semidynamics revolutionized the 64-bit RISC-V processor with cores that are fully customizable using its ‘Open Core Surgery’ approach. This goes deep into the core and is not the tweakable approach typically found in IPs. Combining our technologies now enables multi-core chip designs to be created on this fully coherent RISC-V/CHI platform and then prototyping on an FPGA to demonstrate the integrated performance. We have fully tested them together to ensure compatibility and minimization of verification time.”

SignatureIP www.signatureIP.ai

Founded in 2021, Signature IP develops advanced Network-on-Chip (NoC) solutions that form the basis for a comprehensive platform for SoC design. Our team boasts over 120 person-years of engineering leadership, specializes in interconnect, networking, datacenter, storage and connectivity IP, from specification to production. Our mission at Signature IP is to speed SoC design by easily enabling modifications the NoC topology, various configuration settings, and instant result simulations. Once customers are ready to prototype or implement the NoC, our pushbutton RTL generation integrates directly with customers’ EDA and FPGA environments. Our SaaS tool architecture simplifies tool access and minimizes the burden on their IT department.

Semidynamics www.semidynamics.com

Founded in 2016 and based in Barcelona, Spain, Semidynamics™ is the only provider of fully customisable RISC-V processor IP and specialises in high bandwidth, high performance cores with vector units targeted at machine learning and AI applications. The company is privately owned and is a strategic member of the RISC-V Alliance.

Related Semiconductor IP

- RISC-V IOPMP IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- 64-bit RISC-V core with in-order single issue pipeline. Tiny Linux-capable processor for IoT applications.

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

Related News

- YorChip, Inc.使用巴塞罗那 RISC-V IP领军企业Semidynamics的IP 方案,推出首款用于边缘 AI 应用的小芯片

- Andes晶心科技宣布推出 1024 位RISC-V多核矢量处理器AX45MPV

- 晶心与您相约在RISC-V 峰会; 了解唯一通过ISO 26262标准并完全兼容的 RISC-V CPU以及最新多核 4 路乱序处理器和多核 1024 位向量处理器

- Semidynamics宣布推出RISC-V市场上最大的、完全可定制的矢量单元