stereo 3D 360 stitching IP

Filter

Compare

37

IP

from

10

vendors

(1

-

10)

-

Stereo 3D depth value Correspondenc calculation with 64 disparities

- Stereo Correspondence Calculation

- 64 Disparities

- 75MSampes/sec

- 1 Depth Value per cycle

-

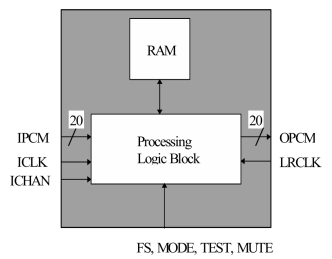

3-D Audio Processing Core

- The J5 is a core cell design of an application specific signal processor which performs both Trusurround(TM) and SRS® 3-D audio virtualization processing in a single design.

- The 3-D processing allows users to enjoy benefits of a multi-channel sound source with only two reporduction channels.

-

-

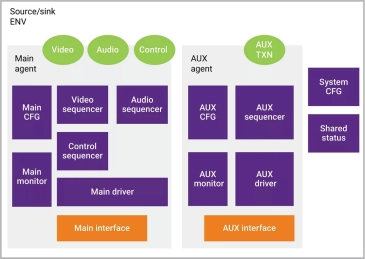

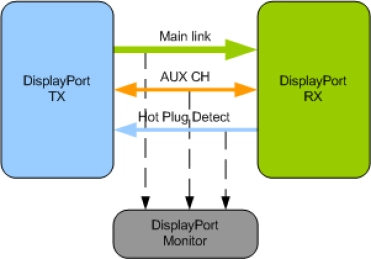

Display Port 2.0 Verification IP

- Full Display port 2.0 source device and sink device functionality.

- Supports backward compatibility with previous versions upto DPv1.4a

- Supports multi lanes upto 4 lanes.

- Supports control symbols for framing.

-

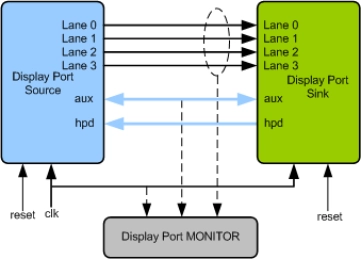

Display Port Verification IP

- Full Display port source device and sink device functionality.

- Display port supports version 1.0,1.1,1.2,1.2a,1.3,1.4,1.4a and 2.0 specification.

- Supports multi lanes upto 4 lanes.

- Supports control symbols for framing(Both Default & Enhanced framing mode).

-

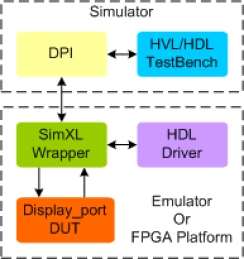

Display Port Synthesizable Transactor

- Supports full Display port source device and sink device functionality

- Supports multi lanes upto 4 lanes

- Supports control symbols for framing(Both Default & Enhanced framing mode)

- Supports interlaced & non-interlaced video stream

-

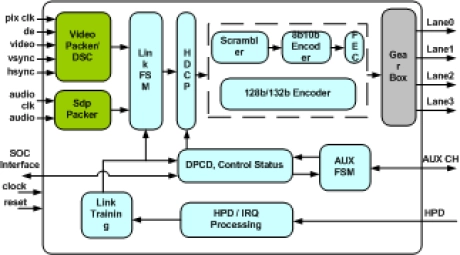

DISPLAY PORT TRANSMITTER IIP

- Compliant with Display Port version 2.0 specification.

- Supports full Display port Transmitter functionality

- Supports multi lanes upto 4 lanes

- Supports 10bit, 20bit, 40bit and 80bit parallel interfaces

-

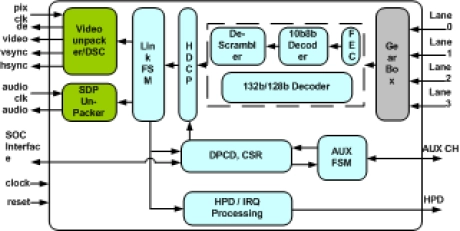

DISPLAY PORT RECEIVER IIP

- Compliant with Display Port version 2.0 specification.

- Supports full Display port Receiver functionality

- Supports multi lanes upto 4 lanes

- Supports 10bit, 20bit, 40bit, and 80bit parallel interfaces

-

DisplayPort 2.0 Verification IP

- Fully compliant to VESA DisplayPort standard 2.0 Specification

- Supports High Bandwidth Digital Content Protection System Version 1.4, 2.2 and 2.3.

- Supports Multi-Stream transport (MST)

- Supports Link Training(LT) tunable PHY Repeaters (LTTPR)

-

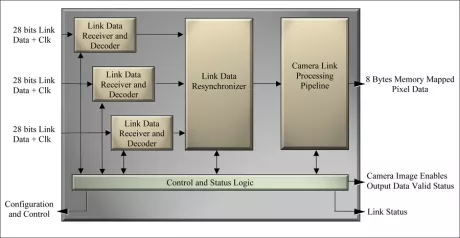

Camera Link Frame Grabber Channel Link Data Processor

- Inclusive of all Camera Link defined camera configurations including the proposed 80 bit extensions which utilize one to three Channel Link or equivalent devices.

- Supports single camera or two independent base cameras for multi-view or 3D stereo applications.

- Fully synchronous pipeline architecture supports high speed implementation in low cost logic devices.

- Dynamic reconfiguration of the processing chain via register interface in addition to a user selected default setup.