Display Port Synthesizable Transactor

Display port Synthesizable Transactor provides a smart way to verify the Display port version upto 2.0 component of a SOC or a AS…

Overview

Display port Synthesizable Transactor provides a smart way to verify the Display port version upto 2.0 component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's Display port Synthesizable Transactor is fully compliant with standard Display port version upto 2.0 Specification and provides the following features.

Key features

- Supports full Display port source device and sink device functionality

- Supports multi lanes upto 4 lanes

- Supports control symbols for framing(Both Default & Enhanced framing mode)

- Supports interlaced & non-interlaced video stream

- Supports nibble interleaving(ECC)

- Supports main link, Aux link and Hot plug functionality

- Supports fast link training

- Supports full link training

- Supports skip the link training

- Supports spread Spectrum clocking (SSC)

- Supports I2C over AUX CH and EDID

- Supports symbol Stuffing and Transfer Unit

- Supports 3D stereo

- Supports ANSI8B10B encoding / decoding

- Supports packing of all the video formats supported by the display port version upto 2.0

- Supports packing of all secondary packet formats supported by the display port version upto2.0

- Supports HPD based link training

- Supports DPCD registers upto display port version 2.0 specification

- Supports RGB, YCBCR444, YCBCR422, YCBCR420 and Y-Only RAW color format

- Supports main stream attribute (MSA) packets

- Supports following Secondary packets,

- Audio timestamp

- Audio stream

- Extension

- Audio copy management

- ISRC

- VSC

- Camera SDP 8 to 15

- Info frame formats

- VSC extension VESA

- VSC extension CEA

- Picture Parameter Set(PPS)

- Adaptive-Sync SDP

- Supports Split SDP for both SST and MST mode

- Supports packing of all audio formats supported by IEC 60958-1,IEC 60958-3,IEC 60958-4,IEC 61937-1,IEC 61937-3,CEA/CTA 861-F,861-G

- Supports training pattern sequence (TPS2,TPS3,TPS4)

- Supports interlane skew insertion in source mode

- Supports deskew in sink device mode

- Supports scrambler as in Display port specification

- Scrambler can be enabled or disabled dynamically

- Supports scrambler reset after every 512th symbol

- Supports on the fly generation of data

- Supports Multi Stream Transport (MST) operation

- Supports Advanced Link Power Management to reduce wake latency

- Supports GTC-based video timing synchronization

- Supports Display Stream Compression (DSC) up to version 1.2a

- Supports Forward Error Correction(FEC)

- Supports 8bit and 16bit RAW interfaces

- Supports 10bit,20bit and 40bit parallel interfaces

- Supports high-bandwidth Digital Content Protection System version1.3 (HDCP v1.3)

- Supports high-bandwidth Digital Content Protection System version2.2 (HDCP v2.2)

- Supports for HDCP2.2 with full authentication

- Supports for HDCP2.2 with bypass the authentication

- Supports High-bandwidth Digital Content Protection System version2.3(HDCP v2.3)

- Detects and reports the following errors

- Invalid control character

- Invalid data character

- Invalid 10bit code

- Sync errors

- Scrambler errors

- Single and multi-bit ECC errors

- Invalid packing injection and detect

- Supports LT-tunable Phy Repeater(LTTPR)

- Supports Horizontal Blanking Expansion

- Supports Jitter insertion for Main Link Clock and Aux Channel Clock

- Supports Ultra-high Bit rates at 10, 13.5, and 20Gbps/lane link rates

- Supports Panel Replay

- Supports 128b/132b channel coding

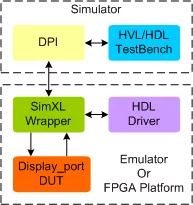

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the Display port testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation also contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Displayport IP core

VESA Adaptive-Sync V2 Operation in DisplayPort VIP

Understanding LTTPR: Enabling High-Speed DisplayPort Interconnects in Complex System Designs

DisplayPort 2025: Navigating the Next Wave of Display Innovation

Audio Transport in DisplayPort VIP

DisplayPort 2.1 vs DisplayPort 1.4: A Detailed Comparison of Key Features

Frequently asked questions about DisplayPort IP cores

What is Display Port Synthesizable Transactor?

Display Port Synthesizable Transactor is a Displayport IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Displayport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Displayport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.