altera IP

Filter

Compare

339

IP

from

59

vendors

(1

-

10)

-

DDR5/DDR4 and LPDDR5/LPDDR4 EMIF FPGA IP

- DDR4 and DDR5 offer higher bandwidth and improved performance over previous generations, with DDR5 providing further enhancements in speed and power efficiency

- LPDDR4 and LPDDR5 are optimized for low power consumption, making them ideal for embedded applications, with LPDDR5 offering even faster data rates and improved energy management

- When integrated with Altera FPGAs these memory technologies enable faster data processing and more efficient power usage for a wide range of applications including networking, cloud and edge.

-

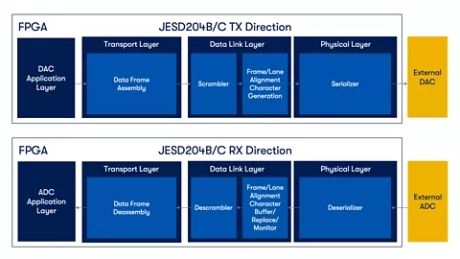

JESD204 FPGA IP

- The JEDEC committee created the JESD204 data converter serial interface standard to standardize and reduce the number of data inputs/outputs between high-speed data converters and other devices, such as FPGAs

- The protocol has many advantages, such as simplified layouts, skew management, and deterministic latency.

-

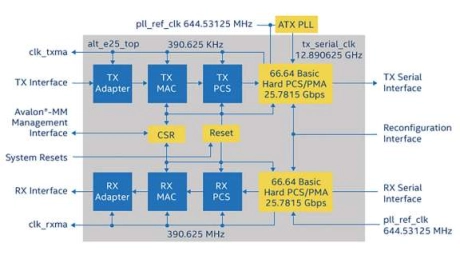

25G Ethernet Intel® FPGA IP

- This IP core implements the 25G and 50G Ethernet Specification, Draft 1.4 from the 25 Gigabit Ethernet Consortium

- The IP core includes an option to support unidirectional transport as defined in Clause 66 of the IEEE 802.3-2012 Ethernet Standard. The media access control (MAC) client side interface for the 25GbE IP core is a 64 bit Avalon® streaming interface (Avalon-ST)

- It maps to one 25.78125 Gbps transceiver

- The IP core optionally includes Reed-Solomon forward error correction (FEC) for support of direct attach copper (DAC) cable.

-

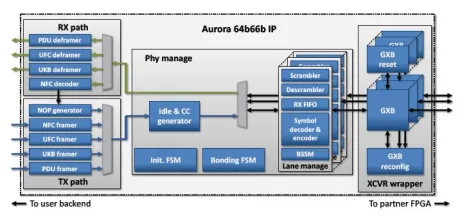

Aurora-like 64b/66b @14Gbps for ALTERA Devices

- Full-Duplex operation.

- Simplex operation.

- Up to 14.1Gbps bit rate per lane

-

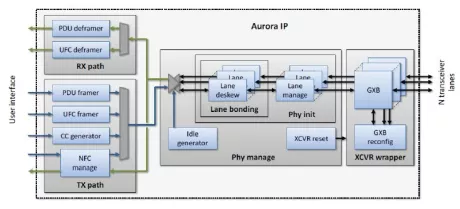

Aurora-like 8b/10b @3Gbps for ALTERA Devices

- Up to 3.125Gbps bit rate per lane

- Configurable up to 16 transceivers lanes

- 8B/10B encoding

- Native flow control with immediate and completion mode

-

Nios® V Processor

- Nios® V processors are the next generation of soft processor IPs, designed to bring the power and flexibility of the open-source RISC-V Architecture to FPGA environments

- By leveraging the RISC-V instruction set architecture (ISA), the Nios V processors offer scalable solutions that enable a spectrum of applications ranging from simple embedded systems to complex, high-performance applications.

-

RLDRAM II Controller Intel® FPGA IP

- Support for industry-standard RLDRAM II components

- Flexible and robust design

- This IP is included in the IP Base Suite which is bundled with Intel® Quartus® Prime Standard and Pro Edition Software.

-

QDR II SRAM Controller Intel® FPGA IP Function

- The QDR II SRAM Controller Intel FPGA IP provides an easy-to-use interface to QDR II SRAM and QDR II+ SRAM modules

- The QDR II SRAM controller ensures that the placement and timing are in line with QDR II specifications

- The QDR II SRAM controller’s local interface is compatible with the Intel FPGA Avalon® Memory-Mapped interface, for easy integration into Intel Qsys IP.