UHS-II IP

Filter

Compare

16

IP

from

9

vendors

(1

-

10)

-

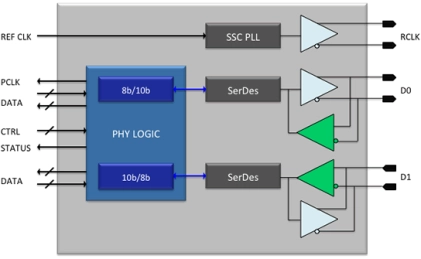

SD4.x UHSII

- Fully compliant with UHSII specification Ver. 4.x

- Bidirectional receiver/transmitter (2 channels) supporting both full and half duplex modes

- Supports data rates from 390Mbps to 1.56Gbps/ch

- RCLK frequency: 26 to 56MHz

- Built-in PLL and clock recovery

-

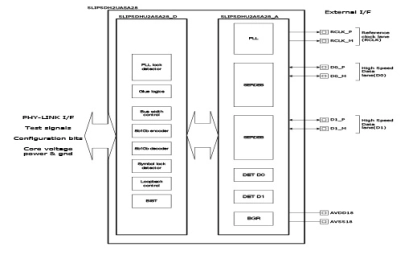

UHS-II PHY Core IP

- The UHS-II PHY IP is a comprehensive, silicon-proven configurable core that has been ported to multiple process nodes and leading foundries.

- It uses sub-LVDS signaling consisting of one pair each for transmit, receive, and an additional reference clock. This low-pin interface has reduced power consumption and low EMI.

- To further reduce power, the reference clock operates at 1/15 or 1/30 of the data transfer speed.

-

UHS-II Device Controller

- Compliance with Part 1 UHS-II Addendum Version 1.02

- Compliance with Part A2 SD Host controller specification version 4.10 & Part1 Physical layer specification version 4.20

- Programmable 1 or 2 Data lane Configuration

- Supports all type of packets

-

SD Card Input/Output Protocol Controller

- Compliance with Embedded MultiMediaCard System Specification Version 4.51. Card support for three different databus modes: 1-bit (default), 4-bit and 8-bit

- Full compatibility with previous versions of MultiMediaCards (backward compatibility)

- Full compliance with SD memory card specifications version 4.2 ( SPI mode and UHS-II mode not supported)

-

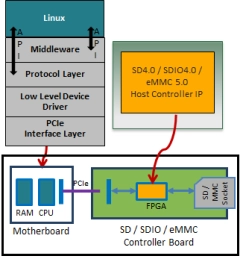

SD 4.1 Hardware Validation Platform

- Designed to be cost-effective and Linux based, this SD 4.1 hardware validation platform (HVP) consists of Arasan’s SD4.0 IP mapped into FPGA’s, offering full speed physical connectivity to a complementary SoC host or memory card device.

-

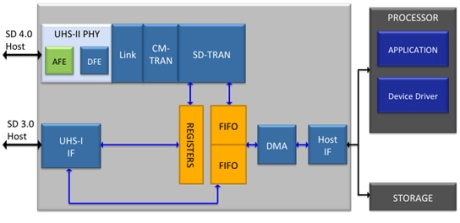

SD 4.1 / SDIO 4.1 / eMMC 4.51 Host Controller IP

- The SD 4.1/SDIO 4.1 IP from Arasan Chip Systems is a highly integrated host controller IP solution that supports three key memory card I/O technologies.

- SD 4.1 Host Controller IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds.

-

SD 4.1 Device Controller IP

- Fully compliant core with proven silicon

- Compliant with SD Specification Part E SD Specification 4.0

- Transfers up to 300 MB/s (UHS156)

- Supports Asynchronous Interrupt to Host controller

- Enhanced power management using new Power

-

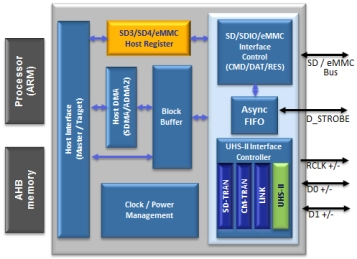

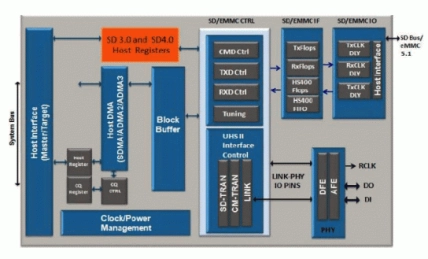

SD 4.1 eMMC 5.1 Dual Host Controller IP

- The SD 4.1/SDIO 4.0/eMMC 5.0 Host IP from Arasan Chip Systems is a highly integrated host controller IP solution that supports three key memory card I/O technologies:

- The SD 4.1 / eMMC 5.1 Host IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds. The IP supports connection to a single slot and performs multi-block writes and erases that lower access overhead. In addition, a host can utilize this IP to boot directly from an attached eMMC memory, thereby simplifying system initialization during power up. The host interface is based on a standard 32-bit AHB bus which is used to transfer data and configure the SD 4.1 / eMMC5.1 Host IP.

- eMMC 5.1 is backward compatible to the previous versions.

-

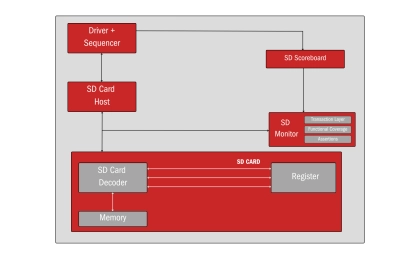

SD Card Controller - Verifies SD card interface functionality, ensuring reliable data transfer and compliance with specifications

- The SD Card Controller Verification IP (VIP) is a tool designed to ensure the proper functionality and performance of SD card memory interfaces in SoCs. It validates key operations like read/write cycles, error handling, and power management across multiple SD card versions.

- This VIP is widely applicable in various fields, from SoC design validation to mobile devices and embedded systems. It guarantees reliable data transfer and smooth integration with SD card interfaces in industries such as automotive, consumer electronics, IoT, and more

-

Simulation VIP for SD CARD and SDIO

- SD Card device standard

- Speed Range A and B

- Default Speed Range A and faster Range B support

- PHY-LINK I/F