SmartDV IP

Filter

Compare

748

IP

from

1

vendors

(1

-

10)

-

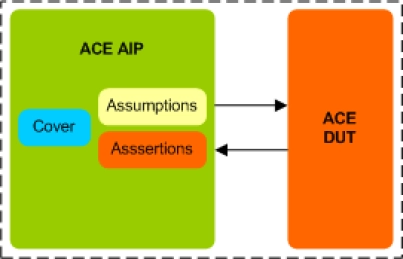

AMBA ACE4 Assertion IP

- Specification Compliance

- Compliant with the latest ARM AMBA ACE4 Protocol Specification.

- Supports all ACE4 data and address widths.

- Supports all protocol transfer types, burst types, burst lengths, burst sizes and response types.

-

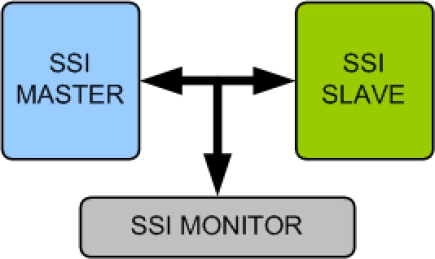

SSI (Synchronous Serial Interface) Verification IP

- Implemented in native OpenVera, Verilog, SystemC and SystemVerilog.

- Supported RVM, AVM, VMM, OVM, UVM and non-standard verify Env.

- Fully compatible with TM4C123GH6PM SSI modules SSI Specification.

- Programmable interface operation for Freescale SPI, MICROWIRE, or Texas Instruments synchronous serial interfaces.

-

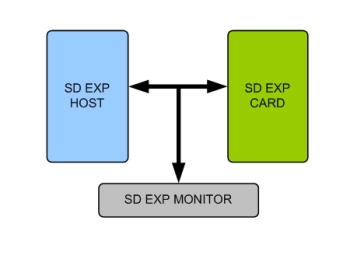

SD Express Verification IP

- Supports SD specification version 7.0, 7.10 and 8.0(Draft) compliant

- SD Express card supports NVMe protocol (revision 1.3, 1.3a, 1.3b, 1.3c, 1.3d and 1.4) over PCIe Interface

- Supports PCI-Express (PCIe) dual simplex point to point serial connection

- Bus Speed Mode - using PCIe Differential Interface lines

-

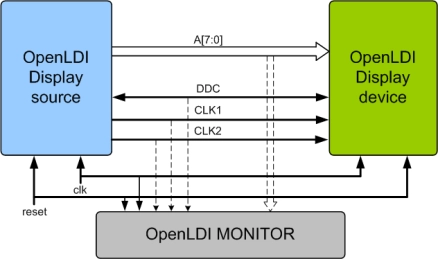

Open LVDS Display Interface (OpenLDI) Verification IP

- Full OpenLDI Display Source and Display Device functionality.

- Supports OpenLDI v0.95 specification

- Supports 8 serial data lines (A0 through A7) and two clock lines (CLK1 and CLK2) in the OpenLDI interface.

- Supports DDC2B protocol to retrieve the EDID data structure from display.

-

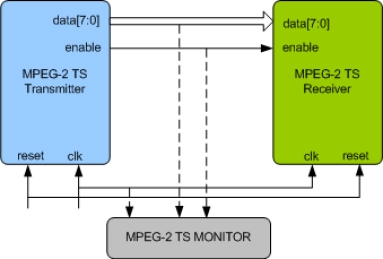

MPEG2TS Verification IP

- Full MPEG-2 TS Transmitter and Receiver functionality.

- Supports the combination of the video and audio coding methods defined in Parts 2 and 3 of ISO/IEC 13818

- Supports Generic coding of moving pictures and associated audio information Part 7 Advanced Audio Coding (AAC).

- Supports Generic coding of moving pictures and associated audio information for Systems as per ISO/IEC 13818-1

-

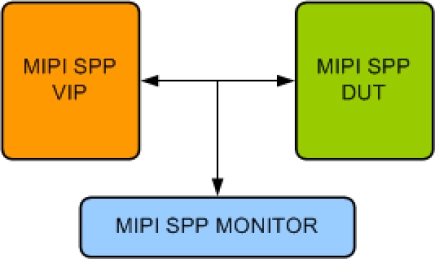

MIPI SPP Verification IP

- Supports version 2.0 Specification.

- Full MIPI SPP Debug Test System (Master) and Target System (Slave) functionality.

- Supports Independent, Full-Duplex Communication.

- Supports dynamic sizing of SPTBs with following types.

-

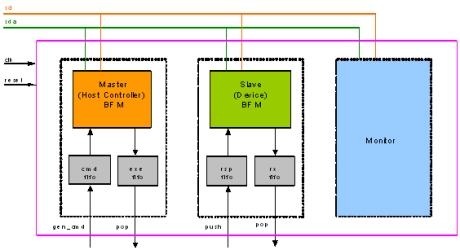

MIPI SoundWire Verification IP

- Full MIPI SoundWire Master, slave and Monitor functionality

- Supports MIPI SoundWire version 1.2r08 Specifications

- Supports Basic PHY and High PHY mode

- Supports IO timing

-

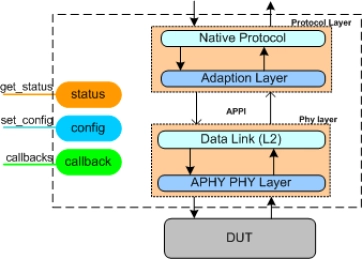

MIPI A-PHY Verification IP

- Implemented in native OpenVera, SystemVerilog, Verilog and SystemC.

- Supported RVM, AVM, VMM, OVM, UVM and non-standard verify env.

- Supports MIPI A-PHY specification version upto 2.0.

- Supports single lane and dual lane, point-to-point and serial communication technology.

-

JESD403 VIP

- Compliant with JESD403 version 1.0 specification.

- Full JESD403 Host Controller and Device functionality.

- Two wire serial interface up to 12.5 MHz.

- Supports Dynamic Address Assignment including Static Addressing for legacy I2C Devices.

-

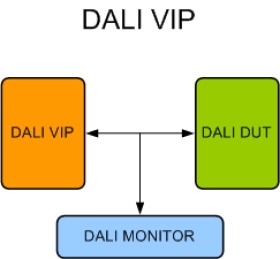

DALI Verification IP

- Complete DALI Tx/Rx functionality.

- Fully configurable serial interface

- Supports programmable clock frequency of operation.

- Configurable baud rate