PCS IP

Filter

Compare

485

IP

from

58

vendors

(1

-

10)

-

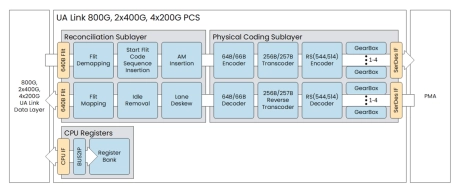

UALink PCS IP Core

- The UA Link PCS IP Core is a high-performance, silicon-agnostic and fully compliant Physical Coding Sublayer (PCS) implementation of UALink_200 specification.

- Designed for seamless integration into accelerator, switch, and SoC designs, it delivers deterministic low-latency, robust error correction, and compatibility with multiple high-speed Ethernet-derived link rates.

-

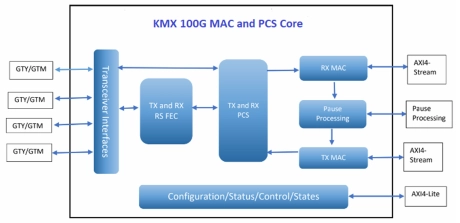

100G MAC and PCS core

- KMX 100G MAC and PCS core, which consists of media access control (MAC) module, physical coding sublayer (PCS) module and physical medium attachment (PMA) module, is compliant with the IEEE 802.3ba-2010 standard.

- The core implements RS FEC as defined in IEEE 802.3bj Clause 91 with independent bit error detection and bit error correction.

-

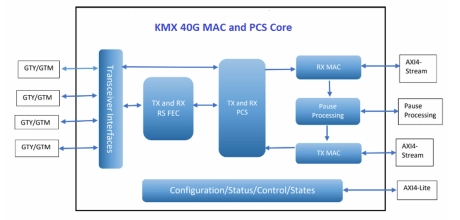

40G MAC and PCS core

- KMX 40G MAC and PCS core, which including media access control (MAC) module, physical coding sublayer (PCS) module and physical medium attachment (PMA) module, is compliant with the IEEE 802.3ba-2010 standard.

- The core supports RS FEC as defined in Clause 74 IEEE 802.3 with independent error bit detection and error bit correction.

-

Ethernet PCS 1G/2.5G/5G/10G/25G & CPRI 7.0

- A combined silicon agnostic implementation of the PCS layer compliant with Ethernet standard IEEE 802.3-2018 and CPRI Specification V7.0 based solution

- The IP-core supports 1G, 2.5G, 5G, 10G, and 25G Ethernet data rates as well as CPRI data rate option 1 (614.14M) to option 10 (24.33024G).

-

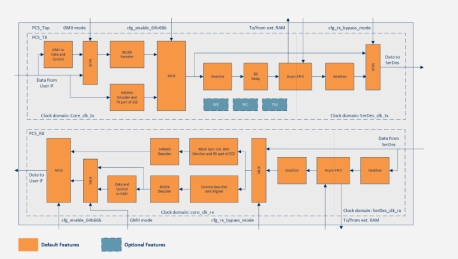

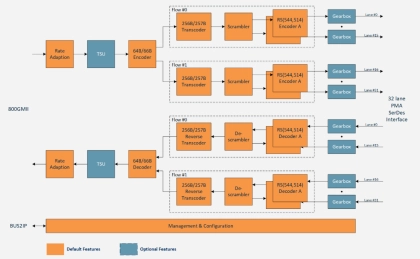

Ethernet PCS 800G

- The 800G Ethernet PCS IP core is a silicon agnostic implementation of the Physical Coding Sublayer (PCS) described in the Ethernet standard IEEE 802.3-2020 and is compliant with Clause 170 and Clause 172 of the IEEE 802.3df specification.

- 800G Ethernet PCS IP provides an interface between the Media Access Control (MAC) and Physical Medium Attachment (PMA) through a 32-lane parallel interface and offers an 800GMII interface on the other side.

-

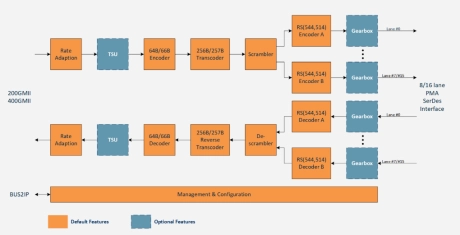

Ethernet PCS 200G/400G

- The 200G/400G Ethernet PCS IP core is a silicon agnostic implementation of the Physical Coding Sublayer (PCS) described in the Ethernet standard IEEE 802.3-2020 and its compliant with Clause 117 and Clause 119 of IEEE 802.3 specification.

- Ethernet PCS 200G/400G IP provides an interface between the Media Access Control (MAC) and Physical Medium Attachment (PMA) through a 8 or 16-lane parallel interface and offers a 200GMII or 400GMII interface on the other side.

-

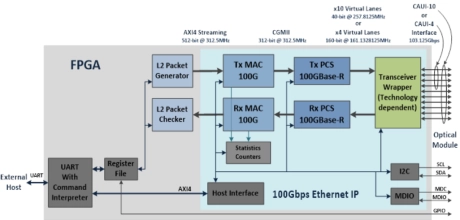

100 G Ethernet MAC & PCS IP Core

- The 100 Gbps Ethernet IP solution offers a fully integrated IEEE802.3ba compliant package for NIC (Network Interface Card) and Ethernet switching applications.

- Ethernet IP solution implements two user (application) side interfaces. The register configuration and control port is a 32-bit AXI4-Lite interface.

-

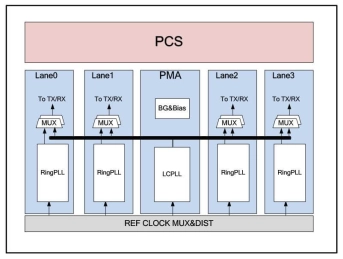

USB3.1 transceiver IP with PMA and PCS layer

- Data rate for Gen 1 physical layer is 5Gbps

- Data rate for Gen 2 physical layer is 10Gbps

- 4 Channel per Quad

- Shared high performance LC tank PLL

-

SATA/SAS 3.0 transceiver IP with PMA and PCS layer

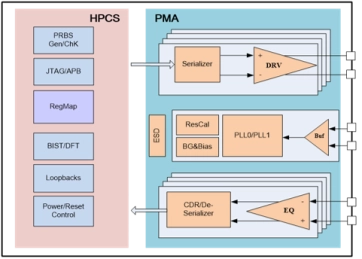

- Highly customizable PMA configuration (controlled by PCS), X4 per Quad

- Support SATA data rate 1.5/3/6Gbps

- Support SAS data rate 1.5/3/6/12Gbps

- Digitally-control-impedance termination resistors

-

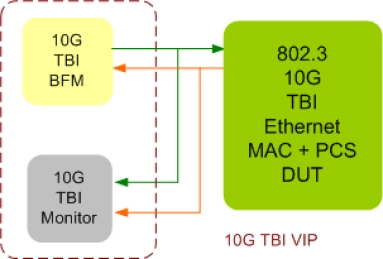

10G TBI (PCS) Ethernet Verification IP

- Follows 10G specification as defined in IEEE 802.3

- Supports all types of 8b/10b PCS TX and RX errors insertion/detection.

- Oversize, undersize, inrange, out of range Packet size errors

- Missing SPD/EPD/SFD framing errors