PCI Express Controller IP

Filter

Compare

389

IP

from

23

vendors

(1

-

10)

-

PCIe - PCI Express Controller

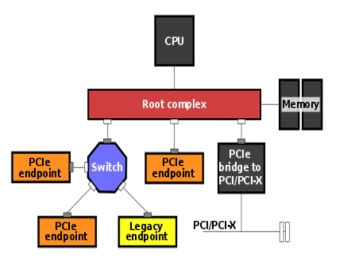

- The PCIe 3.0 (Peripheral Component Interconnect Express 3.0) is a computer hardware interface standard that is used to connect various components to a computer's motherboard.

- It is the third generation of the PCIe standard and offers increased bandwidth, improved performance, and reduced power consumption compared to its predecessor, PCIe 2.0 Overall, PCIe 3.0 provides faster and more efficient communication between the various components in a computer, including graphics cards, network adapters, and storage devices, resulting in better overall performance.

-

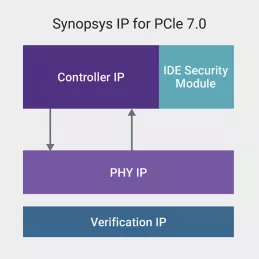

Controller IP for PCI Express 7.0

- Supports all required features of the PCI Express 7.0 (128 GT/s) specification

- Allows a full 128GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

- Advanced RAS-DES features for simplified bring-up and debug

-

Configurable PCI Express 4.0 Link Controller

- Compliant with "PCI Express™ Base Specification, Rev. 4.0 Version 1.0"

- Compliant with "PHY Interface For the PCI Express, SATA, and USB3.1 Architectures"

-

PCI Express to AMBA 4 AXI/3 AXI Bridge

- Complete IP solution consists of digital controllers, PHYs and verification IP

- Fully supports the Synopsys Controller IP for PCI Express Endpoint, Root Port, Dual Mode (EP/RP), and Switch port types

- Fully compliant with the AMBA 3 AXI and 4 AXI interconnects

- Full protocol mapping from PCI Express to the AMBA 3 AXI or 4 AXI bus protocol

-

IDE Security IP Modules for PCI Express 7.0

- Full support of PCI Express 7.0 (64GT/s) IDE specification

- High-performance AES-GCM based packet encryption, decryption, authentication

- Seamless integration with Synopsys controllers via TLP/FLIT packet-based interface

- FLIT mode support

- Support for PCIe 7.0, 6.0, 5.0, 4.0 and 3.1 data rates

-

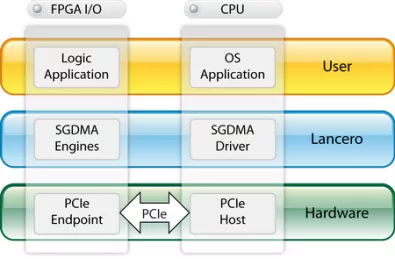

Lancero Scatter-Gather DMA Engine for PCI Express

- PCIe I/O performance: 200 MB/s x1 Gen 1 up to 3360 MB/s x8 Gen 2

- Easily connect logic and high-speed I/O peripherals to PCI Express

- Target Bridge supports Avalon Memory Mapped custom logic

- SGDMA Engine supports Avalon Streaming burst access devices

-

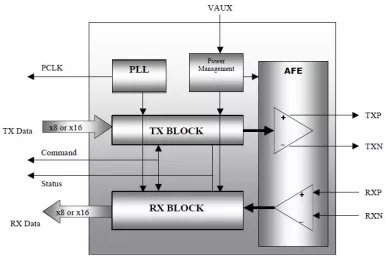

PCI Express PIPE PHY Transceiver

- Supports 2.5Gb/s serial data rate

- Utilizes 8-bit or 16-bit parallel interface to transmit and receive PCI Express data

- Full Support for Auxiliary Power (Vaux) for Energy aware systems like Multi-Port Host Controllers

- Data and clock recovery from serial stream on the PCI Express bus

-

PCI Express Gen5 SERDES PHY on Samsung 8LPP

- Industry leading low power PMA macro – 224mW per lane at 28Gbps (8.0 mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.38 mm2 active silicon area per lane including ESD

- Minimal latency – 3 UI between parallel transfer and serial transmission

- Single-lane macro scalable to unlimited link width – x1, x2, x4, x8, x16, etc.

-

PCI Express Gen4 SERDES PHY on Samsung 7LPP

- Industry leading low power PMA macro – 132.7mW per lane at 16Gbps (8.4mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.32 mm2 active silicon area per lane including ESD

- Minimal latency – 3 UI between parallel transfer and serial transmission

- Single-lane macro scalable to unlimited link width – x1, x2, x4, x8, x16, etc.

-

PCI Express Gen4 / Ethernet SERDES on TSMC CLN5

- Industry leading low power PMA macro – 122.9mW per lane at 16Gbps (7.7mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Support for Ethernet protocols and Automotive Grade 2

- Compact form factor – 0.34 mm2 active silicon area per lane including ESD

- Minimal latency – 3 UI between parallel transfer and serial transmission