PCIe - PCI Express Controller

The PCIe 3.0 (Peripheral Component Interconnect Express 3.0) is a computer hardware interface standard that is used to connect va…

Overview

The PCIe 3.0 (Peripheral Component Interconnect Express 3.0) is a computer hardware interface standard that is used to connect various components to a computer's motherboard. It is the third generation of the PCIe standard and offers increased bandwidth, improved performance, and reduced power consumption compared to its predecessor, PCIe 2.0 Overall, PCIe 3.0 provides faster and more efficient communication between the various components in a computer, including graphics cards, network adapters, and storage devices, resulting in better overall performance.

PCIe 3.0 is a high - speed, bidirectional, and low - cost point-to-point interface that is widely used in PC, consumer electronics, and mobile architectures. It supports dynamic attachment of multiple peripherals to the host via a switch or a bridge. PCIe 3.0 is an open architecture that offers higher data throughput and enables the connection of up to 128 devices to a single port on the motherboard. It is a serial protocol and physical link that transmits data differentially on multiple pairs of wires, while simultaneously providing power to the connected peripherals.

As technology advances, new types of devices, media formats, and storage systems require more bus bandwidth to deliver the desired user experience. In addition, user applications demand faster and more efficient connections between the PC and these increasingly sophisticated peripherals. PCIe 3.0 addresses these requirements by delivering a significantly higher transfer rate that matches the needs of modern usage scenarios and devices. Its increased bandwidth and other features make it an ideal interface standard for meeting the performance demands of modern computer systems.

Product Specifications :

- Fully synthesizable Register Transfer Level (RTL) Verilog HDL core

- Test Bench. (Environment Variable : Verilog)

- Methodologies - based Test Bench : UVM

- Fault Simulation done

- Test Realization in Portable Stimulus Standards (PSS)

- Targeted to Synopsys® Zebu® EP - 1

Product Options :

- Adaptations :

- 8 Bit 8051 Microcontroller Interface available.

- 16 / 32 Bit Standard Microcontroller Interface possible.

- DMA Functionality possible.

- Add - ons : Verification IP - UVM VIP

Key features

- Data transfer rate : PCIe 3.0 supports a data transfer rate of up - to 8 GT / s (gigatransfers per second), which is twice the speed of 2.0.

- Link width : The link width for PCIe 3.0 is up to 16 lanes, which provides a maximum bandwidth of 15.75 GB / s (gigabytes per second) in each direction.

- Lane configuration : PCIe 3.0 has the same lane configuration as its predecessor, PCIe 2.0, with up to 16 lanes. Each lane can provide up to 985 MB / s of bandwidth.

- Increased lane flexibility : PCIe 3.0 also offers increased lane flexibility, allowing the configuration of lanes to be changed dynamically depending on the needs of the system.

- Backward compatibility : PCIe 3.0 is backward compatible with PCIe 2.0 and PCIe 1.0, meaning that devices designed for earlier PCIe versions can be used with a PCIe 3.0 slot, but at a reduced speed.

- Multi - function support : PCIe 3.0 supports multi - function devices, which can provide multiple functions through a single physical device, reducing the need for multiple expansion slots.

- Power consumption : PCIe 3.0 is designed to be more power - efficient than its predecessors, which can help to reduce energy consumption and heat generation.

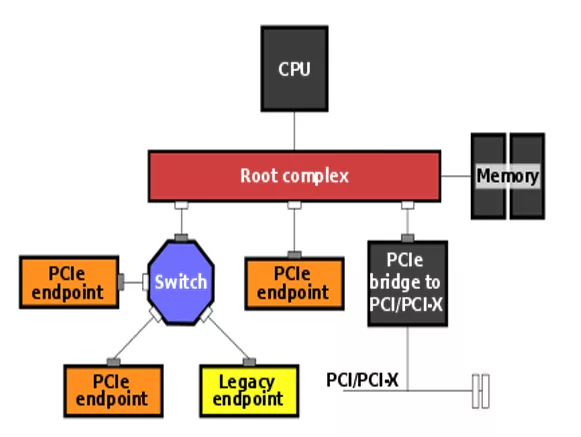

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about PCI Express IP core

How PCI Express Gives AI Accelerators a Super-Fast Jolt of Throughput

PCIe 6.0 - All you need to know about PCI Express Gen6

PCI Express 5 vs. 4: What's New? [Everything You Need to Know]

Complete Interface Solution for PCI Express 5.0 Launched

Doubling Bandwidth in Under Two Years: PCI Express Base Specification Revision 5.0, Version 0.9 is Now Available to Members

Frequently asked questions about PCIe IP cores

What is PCIe - PCI Express Controller?

PCIe - PCI Express Controller is a PCI Express IP core from Silicon Cores - a Div. of Silicon Interfaces listed on Semi IP Hub.

How should engineers evaluate this PCI Express?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PCI Express IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.