Mobile PCIe IP

Filter

Compare

40

IP

from

12

vendors

(1

-

10)

-

PCIe Controller

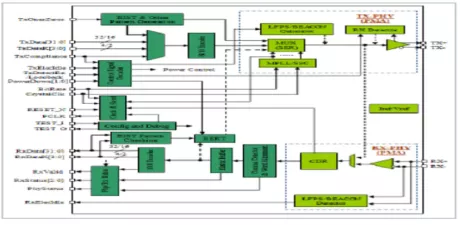

- Dolphin PCIe Controller is a high-performance and compact solution for PCIe provide high-throughput, low-latency, and power-efficient external connectivity in SoCs for mobile, networking, storage, cloud computing, and automotive applications.

- The PCIe Controller consists of silicon-proven digital controllers, PHYs and verification IP, all of which are designed to support all required features of the PCIe 5.0 32GT/s (Gen5), PCIe 4.0 16GT/s (Gen4), 3.1 8GT/s (Gen3), 2.1 5GT/s (Gen2) and 1.1 2.5GT/s (Gen1).

-

PCIe - PCI Express Controller

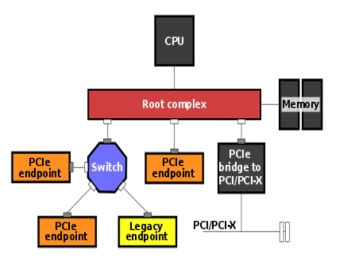

- The PCIe 3.0 (Peripheral Component Interconnect Express 3.0) is a computer hardware interface standard that is used to connect various components to a computer's motherboard.

- It is the third generation of the PCIe standard and offers increased bandwidth, improved performance, and reduced power consumption compared to its predecessor, PCIe 2.0 Overall, PCIe 3.0 provides faster and more efficient communication between the various components in a computer, including graphics cards, network adapters, and storage devices, resulting in better overall performance.

-

10G PHY for PCIe 3.0, TSMC N5 X1, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations

-

10G PHY for PCIe 3.0, TSMC 16FFPLL x8, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations

-

10G PHY for PCIe 3.0, TSMC 16FFPLL x4, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations

-

10G MP PHY for PCIe 3.0/USXGMII/SGMII, TSMC 12FFC x1, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations

-

10G PHY for PCIe 3.0, SS SF5 x2, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations

-

10G PHY for PCIe 3.0, SS SF5 x1, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations

-

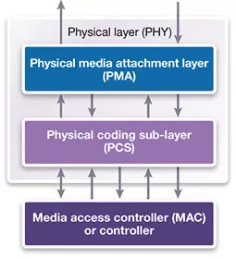

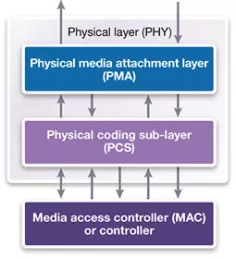

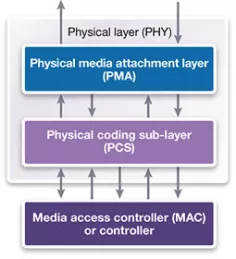

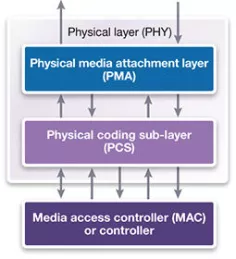

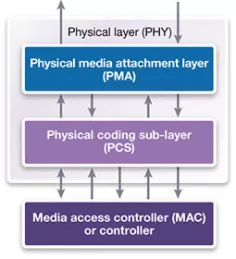

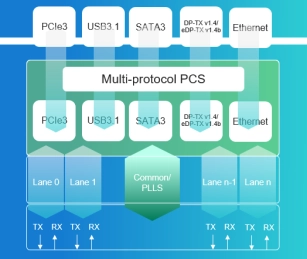

PHY for PCIe 3.1

- Supports PCIe 3.1, USB 3.1, DP-TX v1.4/eDP-TX v1.4b, SATA 3, 10G-KR and QSMII/SGMII

- Multi-protocol support for simultaneous independent links

- Supports SRIS and internal SSC generation

- Supports PCIe L1 sub-states

- Automatic calibration of on-chip termination resistors

- Supports internal and external clock sources with clock active detection

-

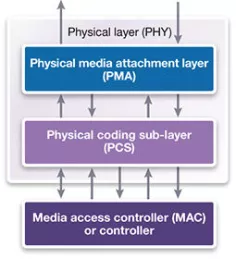

USB 3.0/ PCIe 2.0 Combo PHY IP, Silicon Proven in TSMC 28HPC+

- Standard PHY interface (PIPE) enables multiple IP sources for PCIe/USB3 MAC layer

- Supports 2.5GT/s and 5.0GT/s serial data transmission rate

- Supports 16-bit or 32-bit parallel interface

- Data and clock recovery from serial stream