MPEG-H IP

Filter

Compare

89

IP

from

27

vendors

(1

-

10)

-

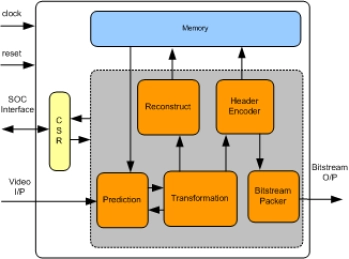

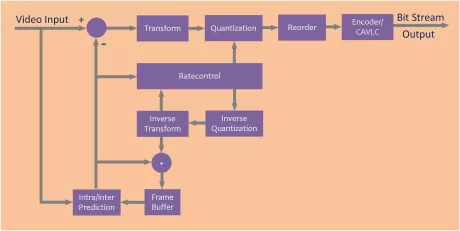

MPEG2 ENCODER IIP

- Supports MPEG-2 standard specification.

- Supports full MPEG-2 encoder functionality.

- Supports video resolution up to 1920x1080@60fps.

- Supports input bit rates up to 100Mbps.

-

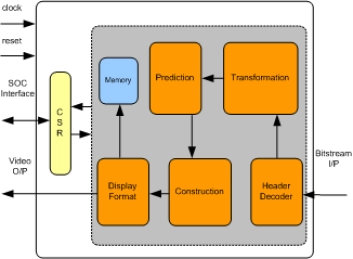

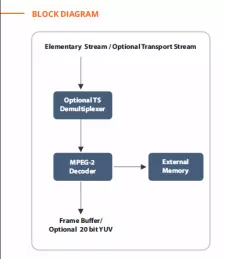

MPEG2 DECODER IIP

- Supports MPEG-2 standard specification.

- Supports full MPEG-2 decoder functionality.

- Supports video resolution up to 1920x1080@60fps.

- Supports input bit rates up to 100Mbps.

-

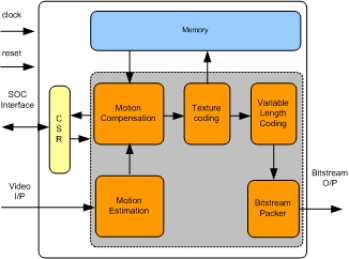

MPEG4 ENCODER IIP

- Supports MPEG-4 standard specification.

- Supports full MPEG-4 encoder functionality.

- Supports YUV 4:2:2 interleaved data as an input.

- Supports image width/height as multiple of 16.

-

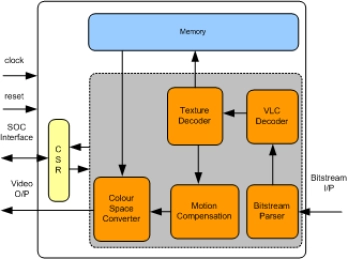

MPEG4 DECODER IIP

- Supports MPEG-4 standard specification.

- Supports full MPEG-4 decoder functionality.

- Supports YUV 4:2:2 interleaved data as an input

- Supports image width as multiple of 16 and height as multiple of 16

-

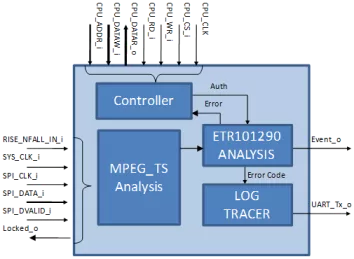

ETR101290 IP core (Checks MPEG TS stream conformity to ETSI TR 101 290 V1.4.1 (2020-06))

- Checks MPEG TS stream conformity to ETSI TR 101 290 V1.4.1 (2020-06)

-

MPEG-2 HD Decoder - Supports 1080p60. 4:2:2. 8-bit,

- Standard: ISO/IEC 13818-2 (H.262)

- Profiles: Simple, Main and 4:2:2

- Video Resolutions: Up to 1920 x 1080

- Frame Rate: Up to 60 fps

-

MPEG-2 Software Video Encoder

- MPEG-2 IPB MP@LL and MP@ML encoding

- Constant bit rate (CBR) and variable bit rate (CBR) support

- YUV 4:2:0 progressive input format

- MPEG-2 compliant transport stream output

-

MPEG TS Deserializer

- Drop-in module for Xilinx Spartan-6, Virtex-6, Artix-7, Kintex-7, Virtex-7, Zynq FPGAs

- Full synthesizable RTL VHDL design (not delivered) for easy customization

-

MPEG TS Serializer

- Drop-in module for Xilinx Spartan-6, Virtex-6, Artix-7, Kintex-7, Virtex-7, Zynq FPGAs

- Full synthesizable RTL VHDL design (not delivered) for easy customization