MIPI MDDI PHY IP

Filter

Compare

754

IP

from

57

vendors

(1

-

10)

-

MIPI RX PHY on SMIC 28nm

- MIPI RX PHY is a mass production IP for D-PHY v1.2 and C-PHY v1.2 protocols

- It includes a total of 5 Lanes, among which there are 4 data lanes and 1 clock lane.

-

MIPI C/D PHY

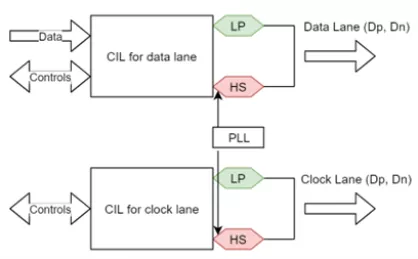

- Compatible with MIPI D-PHY v1.2/CSI-2 protocol

- Up to 4-lane 2.5Gbps/ lane

- Support 2-Lane/4-Lane Application

- Support HS mode (80Mbps to 2.5Gbps per lane) and LP mode (up to 10Mbps)

-

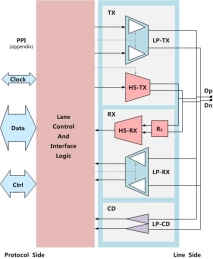

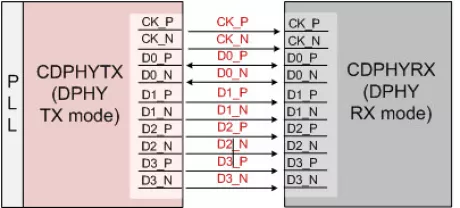

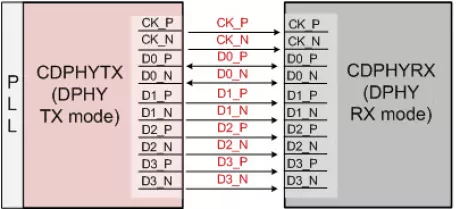

MIPI CD PHY Combo TX & RX + DSI & CSI Controller

- Our MIPI CD-PHY Transmitter and receiver PHY with Display Serial Interface (DSI) and Camera Serial Interface (CSI) Controllers are tailored for high-performance display and camera interface applications.

- These two PHY (TX and RX) integrated systems ensure seamless communication between the processor and display, the processor and camera; supporting high data rates and efficient power consumption.

-

MIPI D-PHY RX 2/4L

- ? Flexible input clock reference - 17 MHz to 27 MHz

- ? 50% DDR output clock duty-cycle

- ? Lane operation ranging from 80 Mbps to 1.5 Gbps in forward direction

- ? Aggregate throughput up to 3 Gbps with two data lanes, 6 Gbps with four data lanes

-

MIPI D-PHY Bidir 2/4L

- ? Attachable PLL clock multiplication unit for master-side functionality

- ? Flexible input clock reference — 5 MHz to 500 MHz

- ? 50% DDR output clock duty-cycle

- ? Lane operation ranging from 80 Mbps to 1.5 Gbps in forward direction

-

MIPI D-PHY TX PHY and DSI controller

- Scalability and Flexibility: Supports multiple data lanes for higher aggregate bandwidth, any of the multiple lanes can be configured into Clock Lane

- High Data Rates: Supports data transmission rates up to 4.5Gbps per lane, allowing for high-resolution displays and smooth refresh rates

- Energy Efficiency: Optimized for low power consumption, making it ideal for battery-powered devices

- Complete Solution: Combines the MIPI D-PHY Transmitter PHY and DSI Controller to make it a one-stop solution

-

MIPI C/D Combo PHY RX - GlobalFoundries 22FDX

- Supports up to one clock lane and four data lanes for DPHY1.2

- Fully compliant with MIPI D-PHY v1.2 and C-PHY v1.0 spec

- Available in GlobalFoundries 22FDX process

- Three 3phase encoded data lanes for CPHY1.0

-

MIPI C/D Combo PHY TX

- Supports HS TX data rate up to 2.5Gbps (2.5Gsps) per lane (trio)

- Fully compliant with MIPI D-PHY v1.2 and C-PHY v1.0 spec

- Available in GlobalFoundries 22FDX process

- Three 3phase encoded data lanes for CPHY1.0

-

MIPI C/D Combo TX PHY and DSI controller

- High Data Rates: Supports data transmission rates

- Energy Efficiency: Optimized for low power consumption, making it ideal for battery-powered devices

- Complete Solution: Combines the MIPI CD-PHY Transmitter PHY and DSI Controller to make it a one-stop solution

- Flexible IP Configuration

-

LVDS/ MIPI Combo PHY IP, Silicon Proven in SMIC 40LL

- GVI

- Support data rate: 0.5Gbps~4.0Gbps

- configurable reference clock frequency

- Per-lane 10-bit/9-bit/8-bit/7-bit parallel interface