MDDI PHY IP

Filter

Compare

7

IP

from

4

vendors

(1

-

7)

-

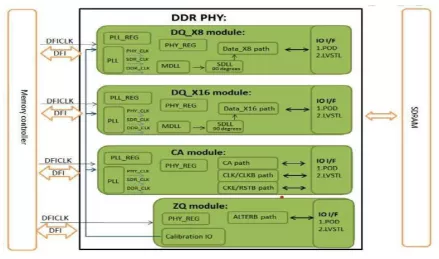

DDR multi PHY

- Compatible with JEDEC standard DDR2/DDR3/LPDDR (or Mobile DDR)/ /LPDDR2/LPDDR3 SDRAMs

- Operating range of 100MHz (200Mb/s) to 533MHz(1066Mb/s) in DDR2/DDR3/LPDDR2/LPDDR3 modes

- Operating range of DC to 200MHz in Mobile DDR mode

- PHY Utility Block (PUBL) component

-

DDR5/DDR4/LPDDR5 Combo PHY IP - 4800Mbps (Silicon Proven in TSMC 12FFC)

- Supported DRAM type: DDR5/DDR4/LPDDR5

- Maximum controller clock frequency of 675MHz resulting in maximum DRAM data rate of 5400MT/s for DDR5

- Maximum controller clock frequency of 400MHz resulting in maximum DRAM data rate of 3200MT/s for DDR4

- Maximum controller clock frequency of 600MHz resulting in maximum DRAM data rate of 4800MT/s for LPDDR5?

-

10/100 Ethernet PHY, TSMC 28nm HPC+

- TSMC 28nm CMOS Logic High Performance Compact Mobile Computing Plus

- Power Supply: 0.9V, 1.8V and 3.3V

- Metal Stack Option:1P8M5X2Z with RDL

- Operating Temperature: -40oC~125oC

-

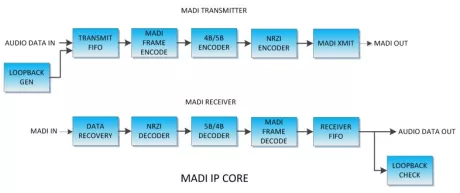

Multi-channel Audio Digital Interface (MADI) IP Core

- No high-speed transceivers required (Hotlink or other)

- Built-in loopback mode with data generation and testing

- Can be configured for number of channels

- Generic FIFO interfaces are provded for the user side interface

-

10/100 Base-TX Fast Ethernet PHY; SMIC 40nm LL

- SMIC 40nm logic Low Leakage Process

- Power Supply: 1.1V and 3.3V

- Minimum metal requirement: 7 metal layers

- Operating Temperature: -40oC~125oC

-

Single port 10/100 Fast Ethernet Transceiver - TSMC12nm FFC

- TSMC12nm FFC

- IEEE 802.3u auto-negotiation, supporting 100Base-TX and 10BASE-T networks over twisted-pair cable in full-duplex or half-duplex mode