LPDDR5x/5/4x/4 PHY IP

Filter

Compare

7

IP

from

2

vendors

(1

-

7)

-

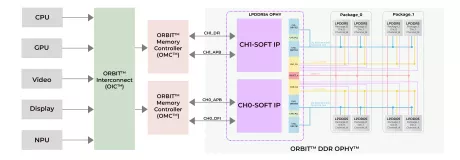

LPDDR5X/5/4X/4 PHY & Controller

- The LPDDR IP includes a LPDDR5X/5/4X/4 Combo PHY and controller.

- It is fully compliant with the JEDEC standard. Optimized for low-power and high-speed applications, it ensures robust timing and a small silicon area.

- The PHY IP contains specialized functions to guarantee high-performance I/Os, critical timing, low power and jitter with programmable fine-grain control for any SDRAM interface.

-

LPDDR5X/5/4X/4 PHY for 16nm

- Compliant with JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports up to 4 ranks

- Multiple frequency states

-

LPDDR5X/5/4X/4 PHY IP for 12nm

- Compliant with JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports up to 4 ranks

- Multiple frequency states

-

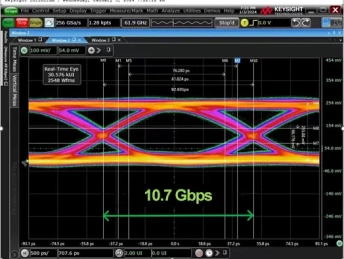

LPDDR5X/5/4X/4 combo PHY at 12nm

- Compliant with JEDEC JESD209-5C for LPDDR5x/5/4x/4 with PHY standards

- Delivering up to 8533Mbps

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

- Multiple frequency states

-

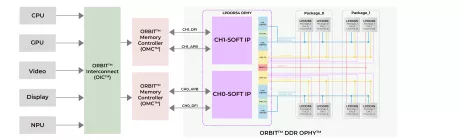

LPDDR5X/5/4X/4 combo PHY at Samsung SF5A

- Compliant for JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

- x16 and x32 channel support

-

LPDDR5X/5/4X/4 combo PHY at 7nm

- Compliant with JEDEC JESD209-5B for LPDDR5X/5/4X/4 with PHY standards

- Delivering up to 8533Mbps

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

-

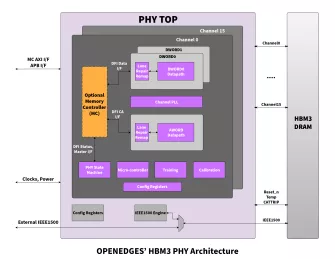

HBM3 PHY IP at 7/6nm

- Compliant with JEDEC JESD238 HBM3

- DFI5.1-based interface with memory controller

- Compliant with ESD requirements

- Supports up to 16-bit independent and asynchronous channel