JESD204B IP

Filter

Compare

111

IP

from

20

vendors

(1

-

10)

-

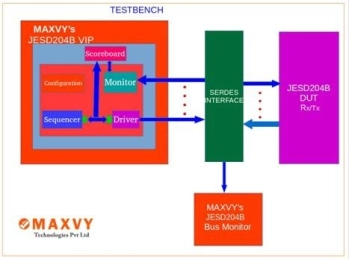

JESD204B UVM VIP

- The vendor provides configurable JESD204B TX/RX verification IP

- JESD204B is a Serial Interface for Data Converters which are defined by JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

- Our VIP covers Transport and Data link layer functionality of JESD204B

- The VIP provides more flexible configuration to user to select their needs like lane,device configuration, data width

-

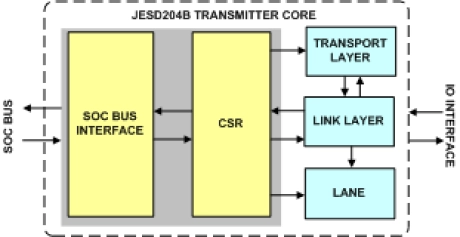

JESD204B Transmitter IIP

- Compliant with JESD204 specification JESD204A, JESD204B.01.

- Full JESD204B transmit functionality.

- Supports data rate upto 12.5 Gbps.

- Supports programmable clock frequency up to 12.5 GHz.

-

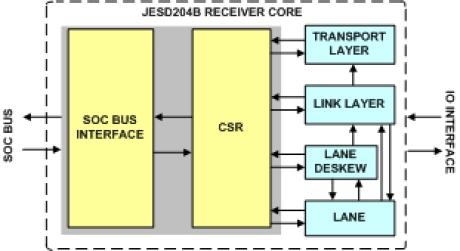

JESD204B Receiver IIP

- Compliant with JESD204 specification JESD204A, JESD204B.01.

- Full JESD204B receive functionality.

- Supports data rate upto 12.5 Gbps.

- Supports programmable clock frequency up to 12.5 GHz.

-

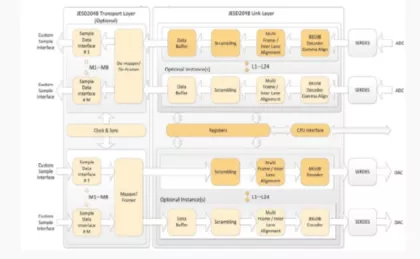

JESD204B Tx-Rx PHY IP, Silicon Proven in TSMC 65GP/55GP

- Widest feature set available in market.

- Scrambling and de-scrambling Included.

- High performance transport layer support.

- Build in test functions

-

JESD204B Tx-Rx PHY IP, Silicon Proven in SMIC 40LL

- Multiple lanes transceiver with data rate from 1Gbps to 16Gbps: Transceiver version including both receiver and transmitter Transmitter only version available

- 40bit/32bit/20bit/16bit selectable parallel data bus Independent per-lane power down control

- Programmable transmit amplitude

- Programmable 3-tap feed forward equalizer (FFE)

-

JESD204B Tx-Rx PHY IP, Silicon Proven in SMIC 28SF

- Multiple lanes transceiver with data rate from 1Gbps to 16Gbps: Transceiver version including both receiver and transmitter

- Transmitter only version available

- 40bit/32bit/20bit/16bit selectable parallel data bus Independent per-lane power down control

- Programmable transmit amplitude

-

JESD204B Tx-Rx PHY IP, Silicon Proven in UMC 55SP

- Multiple lanes transceiver with data rate from 1Gbps to 16Gbps: Transceiver version including both receiver and transmitter

- Transmitter only version available

- 40bit/32bit/20bit/16bit selectable parallel data bus Independent per-lane power down control

- Programmable transmit amplitude

-

JESD204B Tx-Rx PHY IP, Silicon Proven in UMC 28HPC

- Multiple lanes transceiver with data rate from 1Gbps to 16Gbps: Transceiver version including both receiver and transmitter

- Transmitter only version available

- 40bit/32bit/20bit/16bit selectable parallel data bus Independent per-lane power down control

- Programmable transmit amplitude

-

JESD204B Tx-Rx PHY IP, Silicon Proven in SMIC 14SF++

- Multiple lanes transceiver with data rate from 1Gbps to 16Gbps: Transceiver version including both receiver and transmitter

- Transmitter only version available

- 40bit/32bit/20bit/16bit selectable parallel data bus Independent per-lane power down control

- Programmable transmit amplitude

-

JESD204B Tx-Rx PHY IP, Silicon Proven in SMIC 12SF++

- Multiple lanes transceiver with data rate from 1Gbps to 16Gbps: Transceiver version including both receiver and transmitter

- Transmitter only version available

- 40bit/32bit/20bit/16bit selectable parallel data bus Independent per-lane power down control

- Programmable transmit amplitude