ISP IP

Filter

Compare

61

IP

from

23

vendors

(1

-

10)

-

Low-Power ISP

- The Image Signal Processing (ISP)-- ISI700 receives camera sensor data via the 4-channel DVP interface

- It is designed for multi-camera, multi-exposure high dynamic range (HDR) image signal processor (ISP) for the mid- to high-end consumer and surveillance market

- The ISI700 offers the following functions: It brings advanced imaging technologies and chromatic aberration correction to provide unrivalled image quality and support to a large number of HDR sensor formats

-

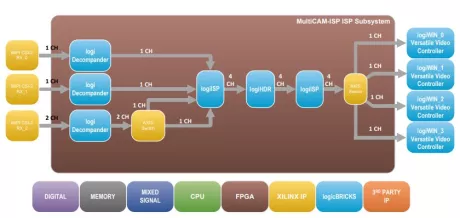

HDR ISP framework for multi-camera applications

- Complete HDR ISP video processing framework for multi-channel vision and AI systems

-

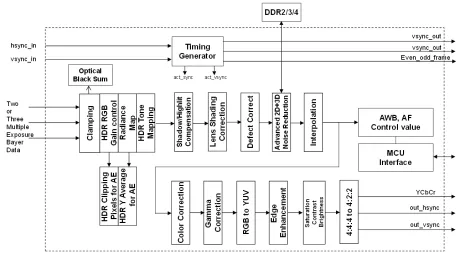

Multiple Pixel Processing Camera Image Signal Processing Core

- Support RGB Bayer progressive image sensor and Monochrome progressive image sensor

- Support 8 ~ 14 bit input data Bayer

-

Small-size ISP (Image Signal Processing) IP ideal for AI camera systems.

- Supporting Formats: MIPI CSI2 UHD 3840x2160@60fps support RAW Bayer / RGGB / RCCB

- Imput / Output Data I/F: AMBA AXI-Stream master/slave protocol

- Register Control I/F: AMBA AXI-Lite

- Supported Device: ASIC / ASSP / SoC / FPGA

-

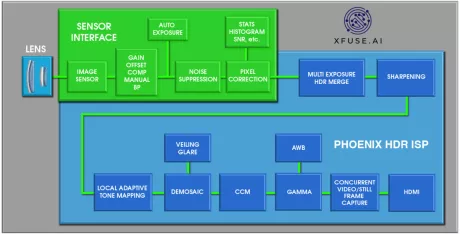

HDR Image Signal Processor

- Advanced motion compensation algorithms virtually eliminate HDR merge artifacts and transition noise

- Proprietary Locally Adaptive Tone Mapping technology

-

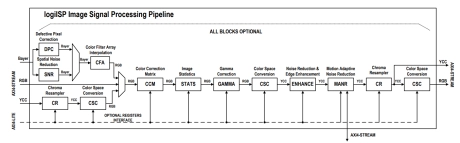

UHD Image Signal Processing (ISP) Pipeline

- The logiISP-UHD Image Signal Processing Pipeline IP core is an Ultra High Definition (UHD) ISP pipeline designed for digital processing and image quality enhancements of an input video stream in Smarter Vision embedded designs based on Xilinx ACAP, MPSoC, SoC and FPGA devices.

- It enables parallel processing of multiple Ultra HD video inputs in different programmable devices, ranging from the small Xilinx Artix®-7 FPGAs to the latest Xilinx Versal Adaptive Compute Acceleration Platform (ACAP) devices.

-

Specialized Video Processing NPU IP for SR, NR, Demosaic, AI ISP, Object Detection, Semantic Segmentation

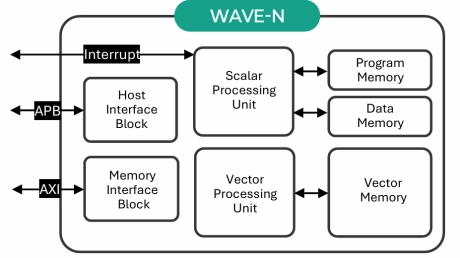

- WAVE-N is a high-performance, video-specialized NPU IP designed to deliver real-time, deep learning-based image enhancement for edge devices.

- By utilizing a proprietary 'Line-by-Line' processing architecture, it significantly reduces DRAM bandwidth and achieves 4x to 10x faster processing speeds compared to conventional NPUs.

-

Image Signal Processor IP - High performance image signal processing for auto and industrial markets

- 32bit DVP interface, 24bit ISP pipeline

- Dual pixel per cycle throughput

- Wide Dynamic Range Tone Mapping (WDR)

- Multi-exposure HDR (Native/build in HDR, Compand output, DOL/Stagger, Stagger output)

-

Image Signal Processor IP - Ultra-low power image signal processing for AIoT and wearable markets

- Supports DVP Input Interface

- Input color formats: 8-bit, 10-bit, 12-bit Bayer; 8-bit, 10-bit YUV BT.601, BT.656; 8-bit, 10-bit monochrome

- SW Register Configuration: 32-bit AHB Slave

- Frame rate control, configurable output FPS range from 60fps to 1fps

-

Image Signal Processor IP enabling high performance real-time image processing

- Support DVP Input Interface

- Support 8-16 Bit Bayer RAW and ITU-R BT.601 & 656 Video Interface

- Test Pattern Generator (TPG)

- Black Level Measurement and Compensation (BLS)

- Sensor Linear Correction