IEEE 802.1AE IP

Filter

Compare

45

IP

from

12

vendors

(1

-

10)

-

IEEE 802.1ae MACSEC IP Core for 40 Gbit Ethernet

- Complies with IEEE 802.1ae standard

- Based on the Algotronix AES-GCM-40G product

- Supports 256 bit keys as standard

- Targets high performance FPGA families from Xilinx and Altera.

-

IEEE 802.1ae MACSEC IP Core for 10 Gbit Ethernet

- Complies with IEEE 802.1ae standard

- Based on the Algotronix AES-GCM-1G product

- Supports 128 bit keys as standard, with 256 bit key option available

- Targets all modern FPGA families from Xilinx, Altera, Microsemi and Lattice

-

Multiple SecY IEEE 802.1ae MACSEC IP Core for 40Gbit Ethernet

- Complies with IEEE 802.1ae standard

- Based on the Algotronix AES-GCM-1G product

- Supports 128 bit keys as standard, with 256 bit key option available

- Targets all modern FPGA families from Xilinx, Altera, Microsemi and Lattice

-

IEEE 802.1ae (MACsec) 100G Security Processor with Avalon-ST Interface

- Small size combined with high performance

- Self-contained

- Very low latency

-

IEEE 802.1ae (MACsec) Security Processor

- Small size combined with high performance:

- Self-contained, uses two external memories for key storage and statistic counters

- Very low latency

- Back-to-back packet processing

-

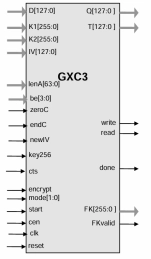

AES-GCM MACsec (IEEE 802.1AE) and FC-SP Cores

- Small size: Starting at less than 13K ASIC gates, 1.5 Gbps performance at less than 20K gates

- Scalability to throughputs of 128 bits per clock with the capability of parallel cores at throughputs of 100 Gbps and above

- Supports Galois Counter Mode Encryption and authentication (GCM-AES a.k.a. AES-GCM)

- Includes AES-GCM encryption, AES-GCM decryption, key expansion and data interface

-

P1619 / 802.1ae (MACSec) GCM/XTS/CBC-AES Core

- Small size: From 70K ASIC gates (at throughput of 18.2 bits per clock)

- 500 MHz frequency in 90 nm process

- Easily parallelizable to achieve higher throughputs

- Completely self-contained: does not require external memory. Includes encryption, decryption, key expansion and data interface

-

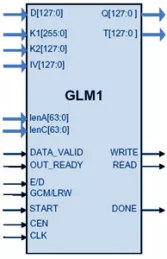

Combo P1619 / 802.1ae (MACSec) GCM-AES/LRW-AES Cores

- Small size: from 31,000 ASIC gates for GLM1 from 58,000 ASIC gates for GLM2

- 400 MHz frequency in 130 nm process GLM1 throughput is 12.8 bits per clock GLM2 throughput is 25.6 bits per clock

- Easily parallelizable to achieve higher throughputs

- Completely self-contained: does not require external memory. Includes encryption, decryption, key expansion and data interface

-

HPC MACsec Security Modules for Ethernet

- IEEE 802.1ae, IEEE 802.1br Support

- 100 Gbps—1.6 Tbps

- Can reach higher throughputs scalable to 3.2 Tbps

- Supports also lower performance modes down to 10 Gbps

-

ASIL B / ISO 26262 and ISO 21434 Compliant 1G-25G MACsec Security Module

- Synopsys MACsec Security Modules use scalable AES-GCM cryptography to provide confidentiality, integrity, authentication, and replay protection for Ethernet traffic.

- These modules integrate seamlessly with Synopsys Ethernet MAC & PCS IP, supporting high data rates with low latency. By incorporating Synopsys MACsec Security Modules into Ethernet IP solutions, networking SoC designers can ensure end-to-end security for data in motion between Ethernet-connected devices.