World First: Synopsys MACsec IP Receives ISO/PAS 8800 Certification for Automotive and Physical AI Security

Synopsys MACsec IP sets a new standard for automotive AI safety with ISO/PAS 8800 certification, delivering secure, real-time vehicle data.

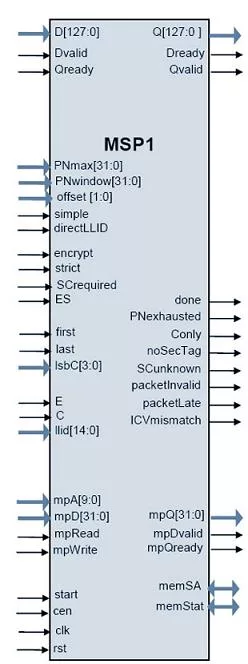

Implementation of the new LAN security standard IEEE 802.1ae (MACsec) requires the NIST standard AES cipher in the GCM mode for e…

Note: some files may require an NDA depending on provider policy.

IEEE 802.1ae (MACsec) Security Processor is a MACsec IP core from IP Cores, Inc. listed on Semi IP Hub.

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MACsec IP.

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.