DDR2 DDR3 IP

Filter

Compare

28

IP

from

14

vendors

(1

-

10)

-

Performance Enhanced version of uMCTL2 supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3 and LPDDR2 for Automotive

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

Performance Enhanced version of DDR Enhanced Memory Ctl (uMCTL2) supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3, and LPDDR2

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

DDR Enhanced Protocol Controller (uPCTL2) supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3, and LPDDR2

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

High Performance DDR 3/2 Memory Controller IP

- Supports DDR3/DDR2 SDRAM

- 16 bits width DDR2/DDR3 SDRAM Interface

- Memory Clock up to 462MHz, DFI Clock up to 462MHz

- Support DDR2 667/800/1066 and DDR3 667/800/1066/1333/1600/1866

-

DDR3/ DDR2 Combo PHY IP - 1866Mbps (Silicon Proven in UMC 40LP)

- Supports DDR3/DDR2 SDRAM

- DDR3 JEDEC standard 1.5v I/O (SSTL_15- compatible)

- DDR2 JEDEC standard 1.8v I/O (SSTL_18- compatible)

- 16 bits width, Single Channel DDR3/DDR2 SDRAM Interface.

-

SSTL with bi-directional I/O’s, Vref, and ODT for DDR2 memory (1.8 V)

- • Mode select – DDR2 or DDR3

- • Single-ended and differential signaling

- • DDR2 capability

- o Compliant with JEDEC specification JESD79-2E, DDR2-400

-

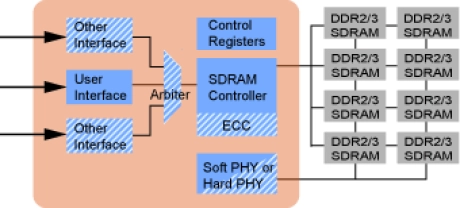

DDR3 SDRAM Controller

- Supports industry standard Double Data Rate (DDR2 and DDR3) SDRAM.

- Pipeline access allows continuous data bursting and hidden command execution.

- Page hit detection supports fast column access and multiple open banks.

- High speed implementation with standard DFI support for hard DDR PHY.

-

DDR3/DDR3L Compatible I/O Buffer on TSMC CLN40G

- High-Speed Bi-directional DDR3/DDR3L compatible I/O buffer

- Operation up to 1066MHz DDR (2133Mbps) performance with single load topology

- Designed with core and 1.8V IO oxide devices

- Built-in ODT (On-Die Termination)

-

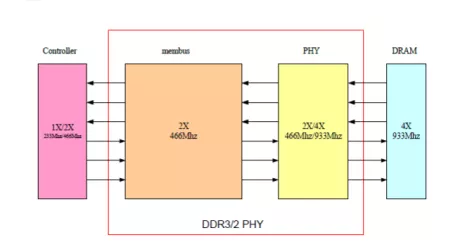

DDR3/2 PHY - TSMC 40LP25

- When combined with a Synopsys DDR memory or protocol controller and verification IP, Synopsys provides a complete DDR3/2 interface IP solution

- Scalable architecture that supports the speed range from DDR2-667 up to DDR3-2133

- Support for DDR3L (1.35V DDR3)

- Support for DDR2 and DDR3 DIMMs

-

DDR3/2 PHY

- ? DDR2/DDR3/DDR3U/DDR3L/LVCMOS operating modes

- ? Compatible with JEDEC standard DDR2/DDR3/DDR3U/DDR3L SDRAMs

- ? Scalable performance from DDR2-667 through DDR3-1600

- ? Maximum controller clock frequency of 400MHz resulting in maximum SDRAM data rate of 1600 Mbps