Compute Express Link IP

Filter

Compare

114

IP

from

9

vendors

(1

-

10)

-

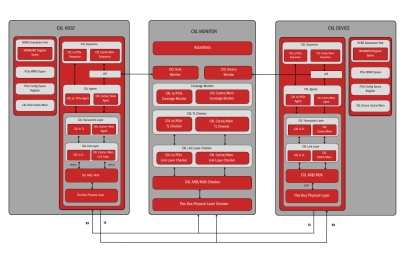

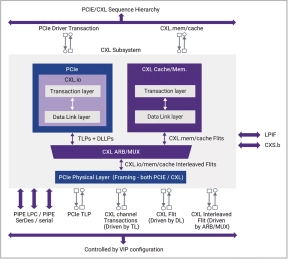

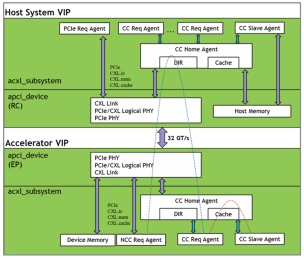

VIP for Compute Express Link (CXL)

- Native SystemVerilog/UVM

- Source Code Test Suites Available

- Built-in Protocol Checks

- Complete Subsystem Verification Solution

-

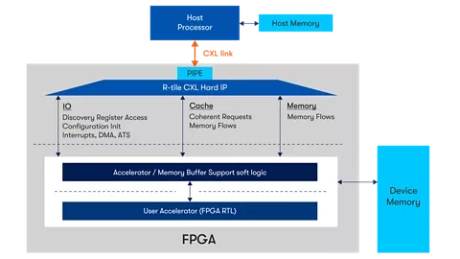

Compute Express Link (CXL) FPGA IP

- Industry's first FPGA-based hardened CXL IP solution for Type 1, 2, and 3 devices.

- First FPGA to pass CXL Consortium Compliance Program (up to 32 GT/s speed).

-

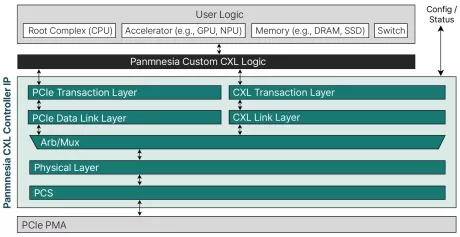

CXL (Compute eXpress Link) 3.1 IP

- Supports all features of the CXL 3.1 specifications and is fully backward compatible with CXL 3.0, 2.0, 1.1, and 1.0 specifications.

-

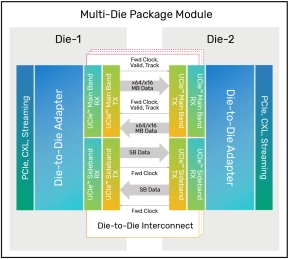

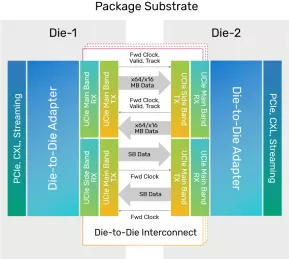

Universal Chiplet Interconnect Express (UCIe™) PHY

- Supports up to 32Gbps per pin including 4/8/12/16/24Gbps

- Forwarded clock, track, and valid pins

- Sideband messaging for link training and parameter exchange

- KGD (Known Good Die) testing capability

- Redundant lane repair (advanced)

- Width degradation (standard)

- Lane reversal

-

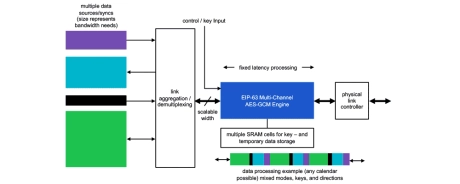

Inline cipher engine for PCIe, CXL, NVMe, 5G FlexE link integrity and data encryption (IDE) using AES GCM mode

- The ICE-IP-63 (EIP-63) is a scalable high-performance, multi-channel cryptographic engine that offers AES-GCM operations as well as AES-CTR and GMAC on bulk data.

- Its flexible data path is suitable to scale from 100 Gbps to 2.4 Tbps to provide a tailored engine with minimal area for your application.

- The FIFO-like data interface makes it possible to perform frame processing for many different protocols, including MACsec, IPsec, and OTN security.

-

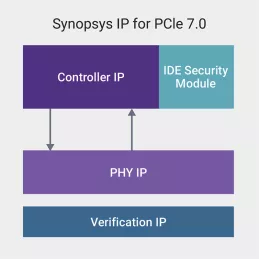

IDE Security IP Modules for PCI Express 7.0

- Full support of PCI Express 7.0 (64GT/s) IDE specification

- High-performance AES-GCM based packet encryption, decryption, authentication

- Seamless integration with Synopsys controllers via TLP/FLIT packet-based interface

- FLIT mode support

- Support for PCIe 7.0, 6.0, 5.0, 4.0 and 3.1 data rates

-

Controller IP for PCI Express 7.0

- Supports all required features of the PCI Express 7.0 (128 GT/s) specification

- Allows a full 128GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

- Advanced RAS-DES features for simplified bring-up and debug

-

Universal Chiplet Interconnect Express (UCIe™) Controller

- Lowest latency controller for data intensive die-to-die applications

- Supports single and multiple PHY modules

- CXS, CHI C2C, AXI, PCIe, CXL, and streaming protocols

- CRC and retry mechanism

- Sideband messaging for link training, parameter exchange, and vendor defined messages

- Link State Management

- Parameter Negotiation

-

Verification IP for CXL

- Accelerated confidence in simulation-based verification of RTL designs with Compute Express Link (CXL) interfaces: CXL1, CXL2, CXL3, CXL3.1

-

CXL - Enables robust testing of CXL-based systems for performance and reliability

- CXL Verification IP is a cutting-edge solution for validating designs based on the Compute Express Link (CXL) protocol. With features like protocol compliance checks, cache coherency validation, and advanced debugging tools, it ensures robust and efficient testing of high-performance computing systems.

- From HPC and AI to automotive and edge computing, CXL Verification IP supports diverse applications. It enables seamless communication between processors, memory, and accelerators, ensuring reliable performance in data centers, ML systems, cloud infrastructures, and telecom networks.