VIP for Compute Express Link (CXL)

Synopsys Verification IP (VIP) for CXL provides verification of design implementations based on CXL specifications which can be u…

Overview

Synopsys Verification IP (VIP) for CXL provides verification of design implementations based on CXL specifications which can be used in SoCs and system level designs to accelerate verification closure. Synopsys VIP provides support for various CXL protocol including CXL.io, CXL.cache, CXL.mem, enabling verification for all device types.

|

Category |

Feature |

|

Specification Version |

CXL 1.1, CXL 2.0, CXL 3.0, CXL IDE, CXL CXS.b, CXL LPIF 1.0, PCIe Base- 5.0/6.0, PIPE- 5.2/6.1 |

|

DUT Configuration |

HOST, Device |

|

Protocol Support |

CXL.io, CXL.cache, CXL.mem, PCIe Only |

|

Interface |

Serial PIPE, SERDES, CXL over CXS ULL, CXL Over CXS LLL |

|

Device Type |

Type 1 – CXL.io + CXL.cache Type 2 – CXL.io + CXL.mem + CXL.cache Type 3 – CXL.io + CXL.mem |

|

Topology |

PCIe TLMs at TL/DL, CXL.io/mem/cache TLM, CXL Flit TLM - CXL Req/ Data/Resp TLM, Logical PHY Interface (LPIF) v 1.1, PCIe LPC, PIPE SerDes Architecture, Serial |

|

Link Speeds |

64 GT/s, 32 GT/s and degraded mode of 16 GT/s and 8 GT/s |

|

Link Width |

Native Width (x16, x8, and x4) and degraded width (x2, x1) |

|

Security |

IDE, DOE |

|

Flit Support |

256B standard, 256B Lopt, 68B, and all other flit types supported for each layer |

|

IO/Cache/Mem |

All types of IO, Cache and Mem Flows, Back-Invalidation Host, Device Bias mode, Retry flow, Viral and Poison, QoS telemetry |

|

ARB/MUX |

All Power Saving states, Weighted Round Robin, Arbitration Bypass mode |

|

Registers |

Configuration Space Registers, Memory Mapped Registers |

|

Flex Bus |

Alternate Protocol Negotiation, Framing Error Handling, Synch Header Bypass |

|

Initialization and Enumeration |

CXL 1.1, 2.0 and 3.0 enumeration, Link Layer Initialization, Bypass Enumeration |

|

Analysis |

Protocol Analyzer, Scoreboard, Protocol Checks at each level, Functional Coverage |

|

Simulator |

Support all Major Simulators |

|

Methodology |

Native SystemVerilog/UVM |

Key features

- Native System Verilog/UVM

- Source code test

- Built-in protocol checks

- Verification plan and coverage

- Verdi protocol-aware debug

- Runs on all major simulators

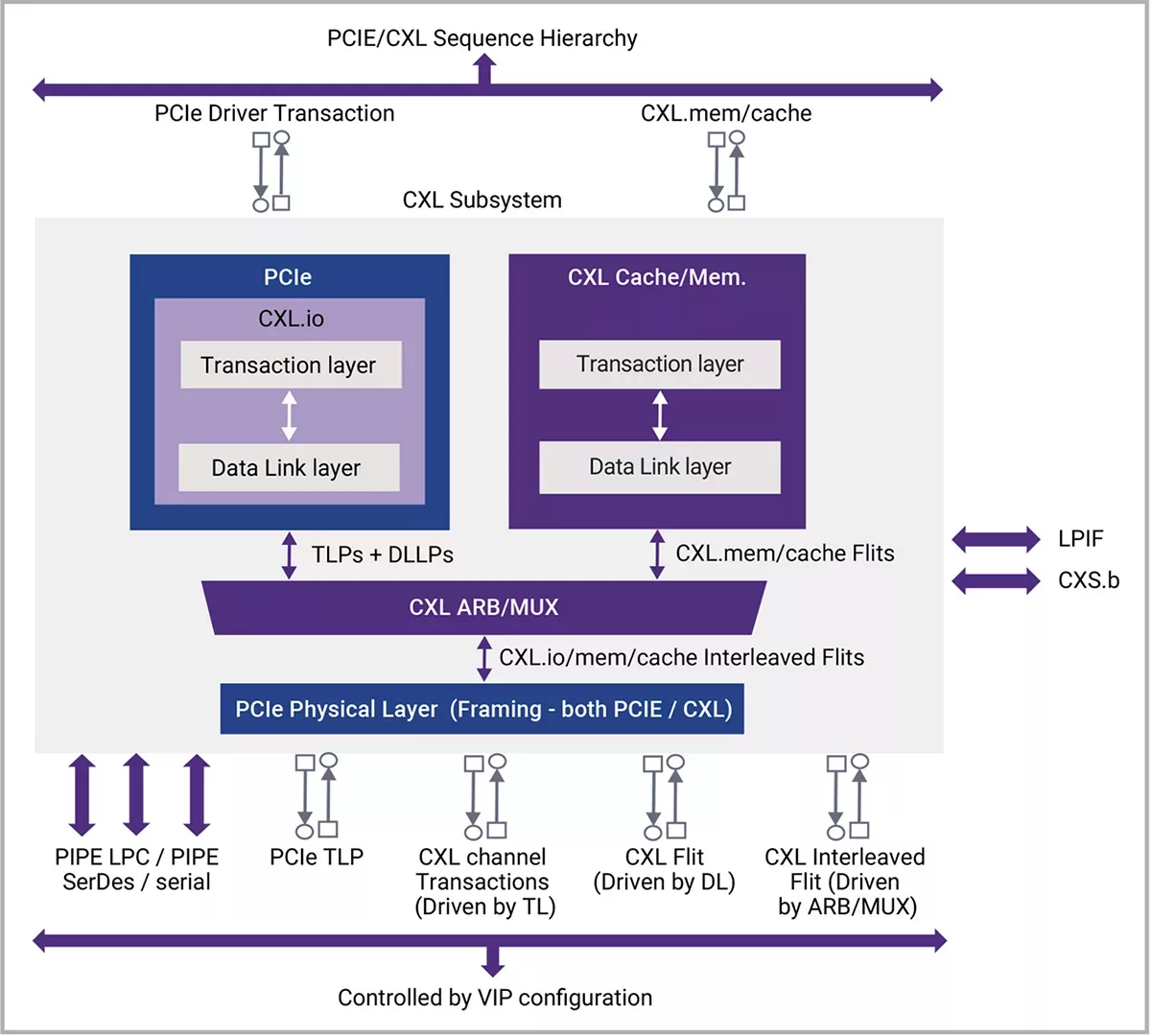

Block Diagram

Benefits

- Native SystemVerilog/UVM

- Source Code Test Suites Available

- Built-in Protocol Checks

- Complete Subsystem Verification Solution

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CXL IP core

Powering Up Efficiency: A Deep Dive into CXL L0p and its Verification

Demystifying CXL Memory Interleaving and HDM Decoder Configuration

From GPUs to Memory Pools: Why AI Needs Compute Express Link (CXL)

cMPI: Using CXL Memory Sharing for MPI One-Sided and Two-Sided Inter-Node Communications

Boosting AI Performance with CXL

Frequently asked questions about CXL IP cores

What is VIP for Compute Express Link (CXL)?

VIP for Compute Express Link (CXL) is a CXL IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this CXL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CXL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.