AI Co-Processor IP

Filter

Compare

17

IP

from

7

vendors

(1

-

10)

-

RISC-V-Based, Open Source AI Accelerator for the Edge

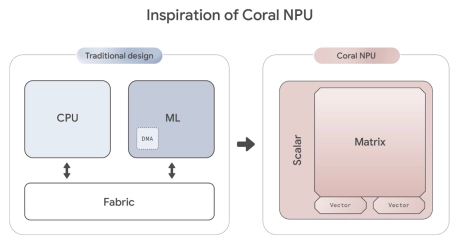

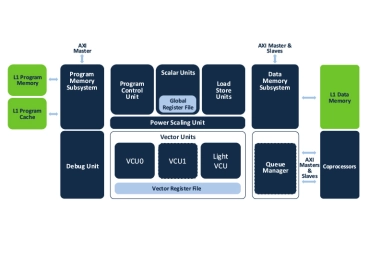

- Coral NPU is a machine learning (ML) accelerator core designed for energy-efficient AI at the edge.

- Based on the open hardware RISC-V ISA, it is available as validated open source IP, for commercial silicon integration.

-

Vision AI DSP

- Ceva-SensPro is a family of DSP cores architected to combine vision, Radar, and AI processing in a single architecture.

- The silicon-proven cores provide scalable performance to cover a wide range of applications that combine vision processing, Radar/LiDAR processing, and AI inferencing to interpret their surroundings. These include automotive, robotics, surveillance, AR/VR, mobile devices, and smart homes.

-

LPDDR5X Secondary/Slave (memory side!) PHY

- JEDEC standard LPDDR5X @ 8533Mbps (Mbits per second per pin)

- Flexible channel architecture – 16- or 32-bit data path widths, supporting either single x32 channel or two x16 channels – 64-bit support, supporting two x32 channels

- Support for byte-mode DRAM devices for high capacity systems

- ZQ Calibration

-

LPDDR5 Secondary/Slave (memory side!) PHY

- JEDEC standard LPDDR5 @ 6400 Mb per second per pin.

- Flexible channel architecture – 16- or 32-bit data path widths, supporting either single x32 channel or two x16 channels – 64-bit support, supporting two x32 channels

- Support for byte-mode DRAM devices for high capacity systems

- ZQ Calibration

-

LPDDR4x Secondary/Slave (memory side!) PHY

- JEDEC standard LPDDR4X @ 4267 Mb per second per pin.

- Flexible channel architecture

-

LPDDR4x/5 Secondary/Slave (memory side!) PHY

- Supports JEDEC standard LPDDR5, LPDDR4X, LPDDR4

- Secondary side PHY

- Custom implementations available

-

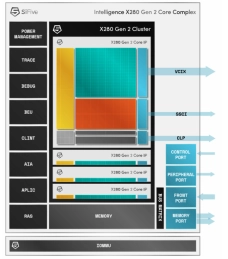

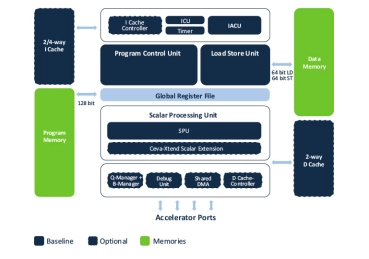

Multi-core capable RISC-V processor with vector extensions

- The SiFive® Intelligence™ X280 Gen 2 is an 8-stage dual issue, in-order, superscalar design with wide vector processing (512 bit VLEN/256-bit DLEN).

- It supports RISC-V Vectors v1.0 (RVV 1.0) and SiFive Intelligence Extensions to accelerate critical AI/ML operations.

-

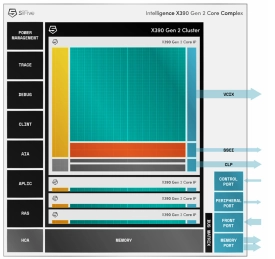

8-stage dual issue, in-order, superscalar processor with dual vector processing units (1024-bit VLEN/512-bit DLEN)

- New RVA23 support

- New RVV1.0 512-bit vector engine

- New SSCI interface added alongside VCIX

- New instructions and extensions

- New improved memory subsystem

-

-

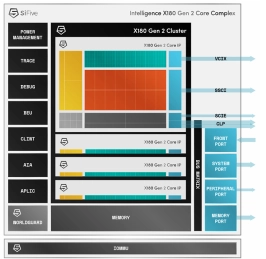

Multi-core capable 64-bit RISC-V CPU with vector extensions

- The SiFive® Intelligence™ X180 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the far edge.

- With this 64-bit version, X100 series IP delivers higher performance and better integration with larger memory systems.