AES LRW IP

Filter

Compare

5

IP

from

2

vendors

(1

-

5)

-

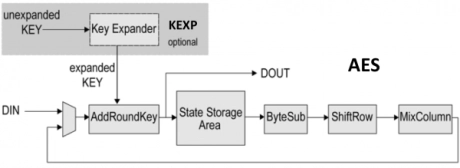

Advanced Encryption Standard Engine

- Encrypts and decrypts using the AES Rijndael Block Cipher Algorithm

- Satisfies Federal Information Processing Standard (FIPS) Publication 197 from the US National Institute of Standards and Technology (NIST)

- Processes 128-bit data in 32-bit blocks

- Employs user-programmable key size of 128, 192, or 256 bits

-

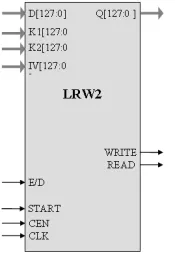

LRW-AES Core

- Small size: LRW3-18.2 starts at less than 50,000 ASIC gates at throughput of 18.2 bits per clock

- Completely self-contained: does not require external memory

- Supports both encryption and decryption

- Includes key expansion

-

LRW-AES Core

- Small size: LRW2-25.6 starts at 44,400 ASIC

- gates at throughput of 25.6 bits per clock.

- Synthesized for 550+ MHz clock speeds

- (70+ Gbps throughput for LRW2-128).

-

LRW-AES Core

- Small size: LRW1 starts at 30,000 ASIC gates at throughput of 12.8 bits per clock

- Synthesized for 600+ MHz clock speeds (70+ Gbps throughput for LRW2-128)

- Completely self-contained: does not require external memory

- Supports Liskov-Rivest-Wagner encryption and decryption (LRW-AES a.k.a. AES-LRW)

-

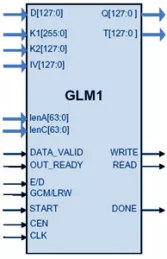

Combo P1619 / 802.1ae (MACSec) GCM-AES/LRW-AES Cores

- Small size: from 31,000 ASIC gates for GLM1 from 58,000 ASIC gates for GLM2

- 400 MHz frequency in 130 nm process GLM1 throughput is 12.8 bits per clock GLM2 throughput is 25.6 bits per clock

- Easily parallelizable to achieve higher throughputs

- Completely self-contained: does not require external memory. Includes encryption, decryption, key expansion and data interface