3GPP IP

Filter

Compare

106

IP

from

31

vendors

(1

-

10)

-

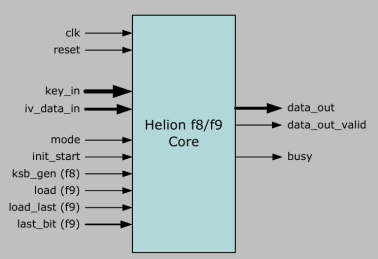

3GPP KASUMI f8 and f9 cores

- The Helion 3GPP KASUMI cores perform the f8 confidentiality and f9 integrity algorithms required to provide data security within the GSM/EDGE and UMTS mobile communication standards.

- Both algorithms are based on the KASUMI 64-bit block cipher which uses a 128-bit key. The KASUMI algorithm was designed by the Security Algorithms Group of Experts (SAGE) within ETSI, and is an optimised version of the MISTY1 block cipher originally developed by Mitsubushi Electric Corporation of Japan. Within ETSI, the f8 and f9 algorithms are now known as UEA1 and UIA1 respectively.

-

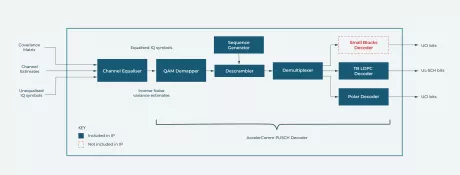

PUSCH Equalizer for 3GPP 5G NR

- Complete implementation of the relevant 3GPP standards

- Improved spectral efficiency across low SINR range against industry-standard simulation toolbox

-

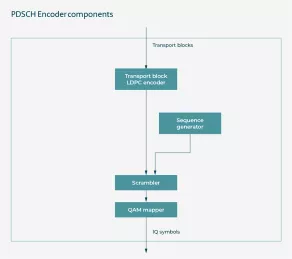

PDSCH Encoder for 3GPP 5G NR

- The PDSCH Encoder and PUSCH Decoder products simplify the creation of high performance 5G NR implementations.

- PDSCH Encoder features the new QAM mapper and Scrambler functionality. These are integrated with LDPC encoder chain and transport block chain components.

- PDSCH encoder has a configurable IQ parallelism for improved performance per clock.

- The functions included are CRC, Segmentation, LDPC encode, Rate matching, Integrated HARQ, Concatenation, Scrambling and Modulation.

-

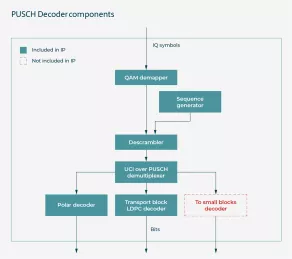

PUSCH Decoder for 3GPP 5G NR

- Complete implementation of the relevant 3GPP standard

- Improved BLER for UCI control data

-

ASIC IP-core for very-high-throughput decoding (>20G) of 3GPP 5G Release 15

- Portable to all ASIC and FPGA technologies

-

3GPP LTE PUCCH Receiver

- Compliant with 3GPP TS36.211 Release 9

- Support for all control formats (1, 1a, 1b, 2, 2a and 2b)

- Support for mixed format

- Support for normal and shortened slots

-

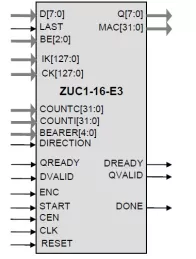

Ultra-Compact 3GPP Cipher Core

- Keystream generation using the ZUC Algorithm version 1.6 (ZUC-2011)

- High throughput: up to 40 Gbps in 65 nm process, 10 Gbps in Altera Stratix III

- Small size: from 7.5K ASIC gates

- Satisfies ETSI SAGE ZUC and EAE3/EIA3 specifications

-

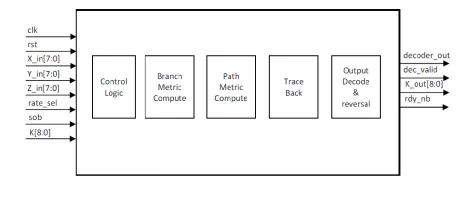

WCDMA Release 9 compliant Viterbi Decoder

- 3GPP TS 25.212 V 9.5.0 Release 9

- Supports all block sizes i.e., K=40 - 504.

- Constraint length of 9

-

High bit rate Turbo Decoder core for 3GPP LTE/ LTE A

- 3GPP LTE/ LTE A compliant

- Implements decoder for requirements as defined in Section 5.1.3.2 of the specification

-

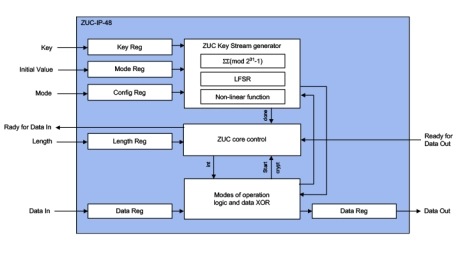

3GPP ZUC Accelerators

- The ZUC-IP-48 (EIP-48) cipher accelerators implement the specification of the 3GPP Confidentiality and Integrity Algorithms as specified by 3GPP and ETSI.

- Designed for fast integration, low gate count and full transforms, the ZUC-IP-48 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high speed SoCs for base stations or other equipment requiring 3GPP support.