Ultra-Compact 3GPP Cipher Core

The ZUC1 core implements ZUC stream cipher in compliance with the 3GPP Confidentiality and Integrity Algorithms 128-EEA3 & 128-EI…

Overview

The ZUC1 core implements ZUC stream cipher in compliance with the 3GPP Confidentiality and Integrity Algorithms 128-EEA3 & 128-EIA3 version 1.6. It produces the keystream that consists of 32-bit blocks using 128-bit key and IV.

Multiple configurations of ZUC1 core are available; the number after dash indicates the throughput in bits per clock, so ZUC1-32 version is 4 times faster than ZUC1-8. Enhanced –E3 version is available that supports both EEA3 and EIA3 confidentiality and integrity algorithms. Compact ZUC1-2-E3 core is very small (12K gates).

The design is fully synchronous and available in both source and netlist form. Test bench includes the ETSI/SAGE test vectors.

Key features

- Keystream generation using the ZUC Algorithm version 1.6 (ZUC-2011)

- High throughput: up to 40 Gbps in 65 nm process, 10 Gbps in Altera Stratix III

- Small size: from 7.5K ASIC gates

- Satisfies ETSI SAGE ZUC and EAE3/EIA3 specifications

- Outputs keystream in 32-bit data blocks

- Uses 128-bit key and IV

- Completely self-contained: does not require external memory

- Available as fully functional and synthesizable Verilog, or as a netlist for popular programmable devices and ASIC libraries

- Deliverables include test benches

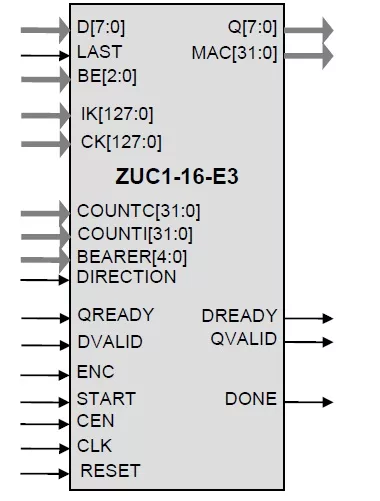

Block Diagram

Applications

- Secure mobile communications

- 3GPP Confidentiality and Integrity Algorithm 128-EEA3 & 128-EIA3

What’s Included?

- HDL Source Licenses

- Synthesizable Verilog RTL source code

- Testbench (self-checking)

- Test vectors

- Expected results

- User Documentation

- Netlist Licenses

- Post-synthesis EDIF

- Testbench (self-checking)

- Test vectors

- Expected results

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Symmetric Crypto IP core

CXL - The Latest Specification in Secured Network Traffic

Securing your apps with Public Key Cryptography & Digital Signature

RoT: The Foundation of Security

Tailoring Root Of Trust Security Capabilities To Specific Customer Needs

Symmetric Cryptographic Offload Options for SoC Designers

Frequently asked questions about Symmetric Cryptography IP cores

What is Ultra-Compact 3GPP Cipher Core?

Ultra-Compact 3GPP Cipher Core is a Symmetric Crypto IP core from IP Cores, Inc. listed on Semi IP Hub.

How should engineers evaluate this Symmetric Crypto?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Symmetric Crypto IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.