1394 PHY IP

Filter

Compare

5

IP

from

4

vendors

(1

-

5)

-

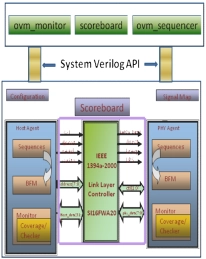

IEEE 1394 OVC

- IEEE 1394a-2000 Link Layer Controller eVC is a fully documented, off the shelf component for Cadence Specman Elite functional verification environment.

- The IEEE 1394 a-2000 link layer controller (from now on referred to only as 1394a) provides connectionless acknowledged data transfer services between a source node and destination node where node is an addressable device attached to the serial bus with at least a minimum set of control registers.

-

FireLink IEEE1394b Link Layer Controller

- IEEE 1394-1995, 1394a-2000 and 1394b-2002 compliant

- Supports 100, 200, 400, and 800Mbps data transfer rates

- Supports Legacy and Beta packets RX/TX (depending on the connected PHY)

- Supports all standard 1394 packet types

-

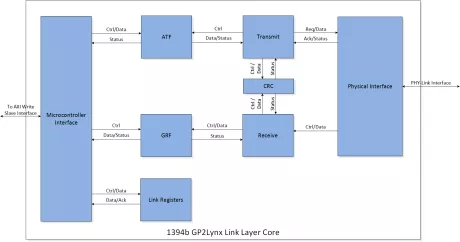

Mil1394 GP2Lynx Link Layer Controller IP Core

- AS5643 compliant interface with hardware-based STOF offload

- Supports S100/S200/S400 data rates

- Configurable number of GP2Lynx nodes in a single FPGA

- Legacy microprocessor or AXI host interface available

-

1394B I/O

- Single-chip solution: The PHY IP can be combined with Link Layer IPs, creating smaller solutions. Additional components can be added to create a System On Chip (SOC) solution.

- Flexible number of ports: Commercially available PHY chips have a fixed number of ports which for small peripherals is often overkill. On the other hand, host adapter would likely benefit from 3 or more ports and a hub could even have more than that. For a PHY based on FPGA technology, the user can customize the number of ports as required.

- Optional debug and test features: Optionally the user can include debug and test features like BERT (Bit Error Rate Test) Low level data monitoring and recording

- Field-upgradable: The used FPGAs are field upgradable thus allowing the addition new features or bug fixes, even if the device is already in the field.

-

Hardware IP Protocol Stack

- Fully-hardware implementation of the standard IP stack avoids the need of extra software development and resulting bottlenecks

- It supports any appliance requiring conversion of data to IP and vice versa

- Transport Streams video flows can be easily adapted to IP transportation

- MindWay provides a complete ecosystem of available Cores that allow you to build lots of IP-based video applications