syn1588® enabled IEEE 1588 compliant clock synchronisation

The syn1588® Clock_M IP core offers the full syn1588® technology with a suitable number of trigger and IO events supported.

Overview

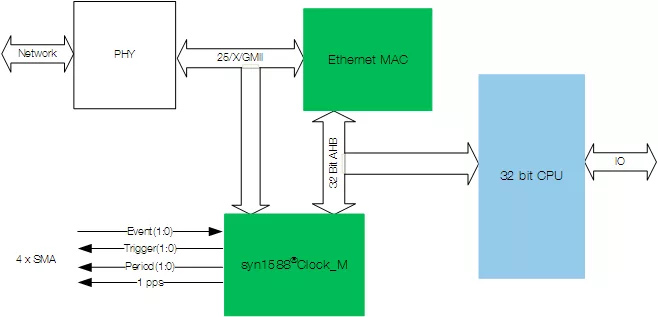

The syn1588® Clock_M IP core offers the full syn1588® technology with a suitable number of trigger and IO events supported. The syn1588® Clock_M IP core is suited for direct integration of a MAC and/or a processor on a single chip (SOC/SOPC design). A standard AHB interface (slave) is available for communication to the host processor executing the PTP Stack.

A typical application example is the syn1588® PCIe NIC. A standard PCIe Ethernet network interface card is made up of a single FPGA that includes the syn1588® Clock_M IP core as well as the Ethernet MAC and the PCIe interface

Key features

- fully synchronous to the system clock

- all registers of the core operate with the rising clock edge

- well commented, structured VHDL source code

- medium footprint and medium I/O count

- AHB type slave interface for clock control using independent CPU clock domain

- media independent interface (MII or GMII) for IEEE1588 message detection

- optional user-programmable time stamper unit

- Oregano Systems‘ patented on-the-fly time-stamping (1-step operation)

- 100/1000 Mbit/s Ethernet interface supported

- 10 Gbit/s Ethernet interface (XGMII)

- New! 25 Gbit/s Ethernet interface (25GMII) available upon request

- two timestamp input signals (EVENT function). One EVENT input offers FIFO to capture dense events. This can be used to synchronize to an external GPS-based time source via a 1 PPS signal. Minimum pulse width is 3 x syn1588® clock period.

- Generation of two a-periodic, one-time events (TRIGGER function). One TRIGGER output offers FIFO to generate dense events. TRIGGERs may be used to start the PERIOD function to allow a precise absolute phase definition in the whole PTP network

- two PERIOD outputs allowing generation of periodical signals (clocks) in a frequency range from mHZ to MHz with a resolution of 2-45 ns

- one 1 pulse per second (PPS) output

- generation of digital IRIG-B output stream (DCLS mode IRIG-B000)

- decoding of digital IRIG-B input stream (DCLS mode IRIG-B000)

- generation of interrupts upon external and internal events

- pipelined adder based clock for best synchronization results

- separate receive and transmit timestamp FIFOs

- clock time format compatible to the IEEE1588 standard

- suited for FPGA as well as ASIC implementations

- optional SMPTE 2059 compatible signal generation

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about IEEE-1588 / PTP IP core

Frequently asked questions about Time Synchronization IP cores

What is syn1588® enabled IEEE 1588 compliant clock synchronisation?

syn1588® enabled IEEE 1588 compliant clock synchronisation is a IEEE-1588 / PTP IP core from Oregano Systems listed on Semi IP Hub.

How should engineers evaluate this IEEE-1588 / PTP?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this IEEE-1588 / PTP IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.