Dual-Port SRAM IP

Welcome to the ultimate Dual-Port SRAM IP hub! Explore our vast directory of Dual-Port SRAM IP

All offers in

Dual-Port SRAM IP

Filter

Compare

124

Dual-Port SRAM IP

from

11

vendors

(1

-

10)

-

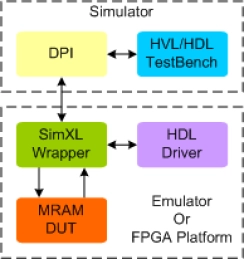

MRAM Synthesizable Transactor

- Supports all the MRAM commands as per the MR2A16A and MR0A08B specifications.

- Supports Symmetrical high-speed read and write with fast access time.

- Supports SRAM Compatible timing

- Supports native non-volatility

-

CodaCache® Last Level Cache IP

- Standalone IP

- 1.2 GHz frequency in 16FF+TT process

- Protocol interoperability: AMBA AXI 4

-

Memory Compiler

- 70-90% power reduction

- Unmatched performance

- Multi-technology support

- Tailored for design needs

-

Serial Peripheral Interface (SPI) Controller

- Dolphin Technology provides Serial Peripheral Interface (SPI) IP which enables an AHB/APB host to access a serial device at high-speed through the SPI interface.

- The controller supports both Master and Slave modes and consists of a DMA controller to enhance the system performance.

- The IP can be used in applications such as flash memory card and digital camera.

-

Memory Compilers

- Dolphin provides a wide range of Memory Compilers and Specialty Memory (ROM, Multi Port RF, CAM, etc.) optimized to meet even the most demanding requirements for high performance, high density and low power.

-

Memory Compilers

- Low Leakage with retention (light and deep sleep)

- Power Gating with retention and without retention

- Dual Rail (SRAM Periphery at lower Voltage)

- Combinations of above low power options

-

Memory Compiler

- High-Density Memory Compilers

- Ultra-High-Speed Memory Compilers

- Low-Power Memory Compilers

-

GF 0.13um Single-Port/Dual-Port SRAM, Single-Port/Two-Port Register File and Diffusion ROM Compiler

- High Density

- High Speed

- Size Sensitive Self-Time Delay for Fast Access

- Automatic Power Down

-

CSMC 0.18um 90% shrunk Single-Port/Dual-Port SRAM, Single-Port/Two-Port Register File and Via1 ROM Compiler

- High Density

- High Speed

- Size Sensitive Self-Time Delay for Fast Access

- Automatic Power Down

-

CSMC 0.13umLP Single-Port/Dual-Port SRAM, Single-Port/Two-Port Register File and Via1 ROM Compiler

- Low Leakage

- High Density

- High Speed

- Size Sensitive Self-Time Delay for Fast Access