MRAM Synthesizable Transactor

MRAM Synthesizable Transactor provides a smart way to verify the MRAM component of a SOC or a ASIC in Emulator or FPGA platform.

Overview

MRAM Synthesizable Transactor provides a smart way to verify the MRAM component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's MRAM Synthesizable Transactor is fully compliant with standard Specification and provides the following features.

Key features

- Supports all the MRAM commands as per the MR2A16A and MR0A08B specifications.

- Supports Symmetrical high-speed read and write with fast access time.

- Supports SRAM Compatible timing

- Supports native non-volatility

- Supports Unlimited read and write endurance

- Supports highly reliable data storage

- Supports the following operating modes

- Byte read

- Byte write

- Output Disabled

- Not Selected

- Supports Flexible data bus control - 8 bit or 16 bit access.

- Supports Flexible density of 4Mb or 16Mb

- Checks for following

- Check-points include power up, initialization and power off rules

- All timing violations

- Supports all types of timing and protocol violation detection.

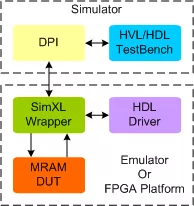

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the MRAM testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and function's used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about MRAM / RRAM IP core

Weebit ReRAM Foundry Developments Presented at FMS

Allowing server-class storage in embedded applications

NVMe IP for Enterprise SSD

Flash Forward: MRAM and RRAM Bring Embedded Memory and Applications into the Future

Assessing Design Space for the Device-Circuit Codesign of Nonvolatile Memory-Based Compute-in-Memory Accelerators

Frequently asked questions about MRAM / RRAM IP cores

What is MRAM Synthesizable Transactor?

MRAM Synthesizable Transactor is a MRAM / RRAM IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this MRAM / RRAM?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MRAM / RRAM IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.