AMBA AXI IP for UMC

Welcome to the ultimate

AMBA AXI IP

for

UMC

hub! Explore our vast directory of

AMBA AXI IP

for

UMC

All offers in

AMBA AXI IP

for

UMC

Filter

Compare

8

AMBA AXI IP

for

UMC

from

2

vendors

(1

-

8)

-

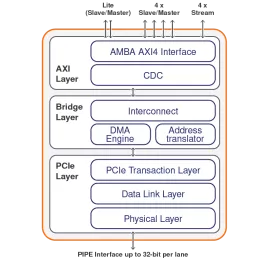

PCIe 3.1 Controller with AXI

- Compliant with the PCI Express 3.1/3.0, and PIPE (16- and 32-bit) specifications

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode configurations

- Supports x16, x8, x4, x2, x1 at 8 GT/s, 5 GT/s, 2.5 GT/s speeds

- Supports AER, ECRC, ECC, MSI, MSI-X, Multi-function, P2P, crosslink, and other optional features

- Supports many ECNs including LTR, L1 PM substates, etc.

-

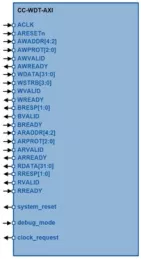

Configurable Watchdog Timer

- AMBA APB4-Lite bus

- Configurable timeout interval

- Standard and windowed mode

- Register write protection

-

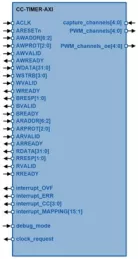

Configurable Timer Counter

- AMBA AXI4-Lite bus

- Programmable multi-function timer

- Double buffered configuration registers

- Configurable single/dual slope PWM outputs

-

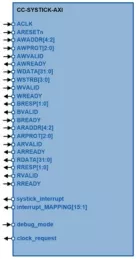

Configurable System Tick Counter

- AMBA APB4-Lite bus

- Programmable system tick timer

- Configurable prescaler and period

- Configurable interrupts

-

SPI Serial Peripheral Interface Master/Slave

- SPI-compatible interface

- AMBA AXI4-Lite bus

- Master or slave mode

- Full duplex

-

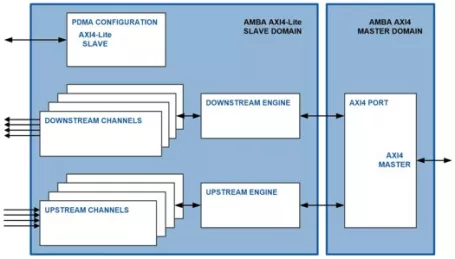

Peripheral Direct Memory Access Controller

- AMBA AXI4-Lite slave bus

- AMBA AXI4 master bus

- Configurable number of peripheral channels

- 8, 16, 32 bits data transfer modes

-

I2C Master Serial Interface Controller

- I2C-compatible interface

- AMBA AXI4-Lite bus

- Standard and custom data rates

- Configurable setup/hold times

-

General Purpose Input/Output Controller

- AMBA AXI4-Lite bus

- Individual configuration of each GPIO pin

- Dynamic programming of each GPIO pin as input or output

- Configurable level or edge triggered interrupts