IP for UMC

Welcome to the ultimate

IP

for

UMC

hub! Explore our vast directory of

IP

for

UMC

All offers in

IP

for

UMC

Filter

Compare

3,057

IP

for

UMC

from

50

vendors

(1

-

10)

-

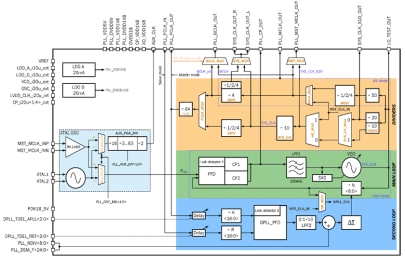

All Digital Fractional-N PLL for Performance Computing in UMC 40LP

- Fractional multiplication with frequency up to 4GHz

- Low jitter (< 10ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 5mW)

-

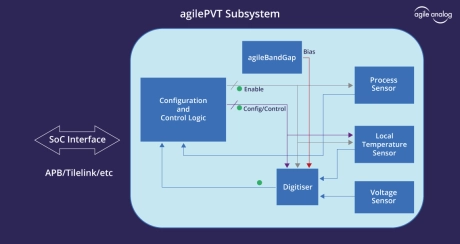

PVT Sensor Subsystem

- Start-up time: Typ 20us

- Current consumption: Max 25uA

- Industry standard digital interface

- Fully integrated macro

- Standard AMBA APB interface

-

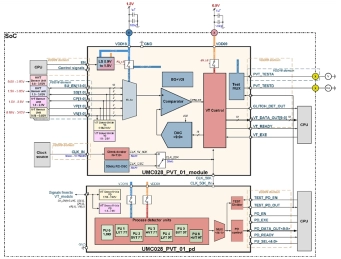

Process/Voltage/Temperature Sensor (Supply voltage 1.8V/0.9V)

- UMC 28nm HPC+ technology

- Temperature measurement range -40°C ÷ +125°C

- Core and IO Voltage measurement range: 0.58V÷0.92V, 1.0V÷2.0V, 1.5V÷3.63V and 0.8÷3.63V

- High accuracy temperature and voltage measurements

-

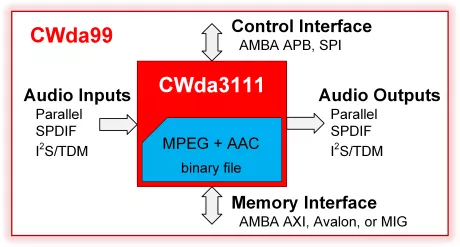

MPEG-1/2 + AAC Audio Decoder

- The MPEG-1/2+AAC Audio Decoder (CWda99) is an audio IP core for decoding up to 6 audio channels in real-time.

- This core contains the MPEG + AAC decoder software and the Coreworks processor based hardware audio engine platform (CWda3111).

-

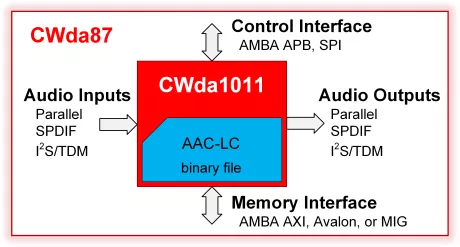

AAC-LC Audio Decoder

- The AAC-LC Audio Decoder (CWda87) is an audio IP core for decoding up to 6 audio channels in real-time.

- This core contains the AAC-LC decoder software and the Coreworks processor based hardware audio engine platform (CWda1011).

-

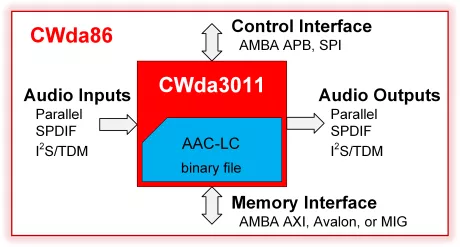

AAC-LC Audio Encoder

- The AAC-LC Audio Encoder (CWda86) is an audio IP core for encoding up to 6 audio channels in real-time.

- This core contains the AAC-LC encoder software and the Coreworks processor based hardware audio engine platform (CWda3011).

-

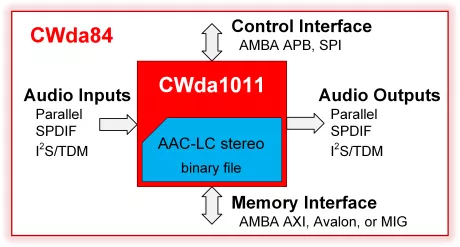

AAC-LC Stereo Audio Encoder

- The AAC-LC Stereo Audio Encoder (CWda84) is an audio IP core for encoding one stereo stream in real-time.

- This core contains the AAC-LC stereo encoder software and the Coreworks processor based hardware audio engine platform (CWda1011).

-

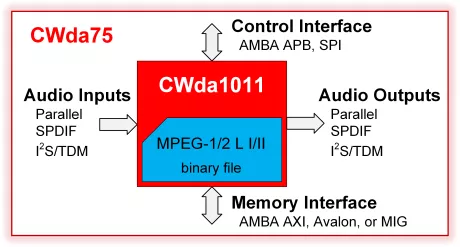

MPEG-1/2 – Layer I/II Audio Decoder

- The MPEG-1/2 – Layer I/II Audio Decoder (CWda75) is an audio IP core for decoding one audio stream in real-time(1).

- This core contains the MPEG-1/2 – Layer I/II decoder software and the Coreworks processor based hardware audio engine platform (CWda1011).

-

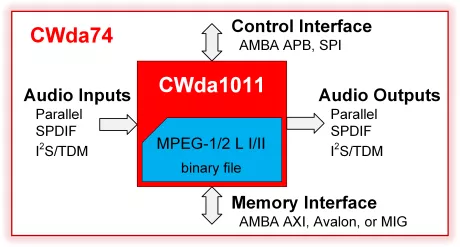

MPEG-1/2 - Layer I/II Audio Encoder

- The MPEG-1/2 – Layer I/II Audio Encoder (CWda74) is an audio IP core for encoding one audio stream in real-time.

- This core contains the MPEG-1/2 – Layer I/II encoder software and the Coreworks processor based hardware audio engine platform (CWda1011).

-

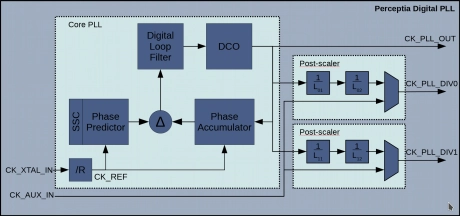

2.26GHz/2.46GHz Fractional-N LC Phase-Locked Loop with oscillator

- 180XFAB_PLL_01 uses 2.25792GHz/2.4576GHz Phase locked loop frequency synthesizer for clock generation.

- It consists of the following main sub-blocks: reference oscillator; main PLL loop: Fractional-N PLL and VCO blocks; secondary digital PLL loop: synchronization subsystem; dividers block: clock generation/delivery subsystem; voltage stabilizers.

- High frequency synthesis is needed for both phase noise performance and ultra-fine frequency tuning step.