AMBA AHB / APB/ AXI IP for TSMC

Welcome to the ultimate

AMBA AHB / APB/ AXI IP

for

TSMC

hub! Explore our vast directory of

AMBA AHB / APB/ AXI IP

for

TSMC

All offers in

AMBA AHB / APB/ AXI IP

for

TSMC

Filter

Compare

1

AMBA AHB / APB/ AXI IP

for

TSMC

from

1

vendors

(1

-

1)

-

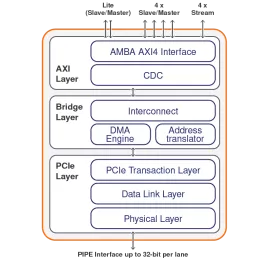

PCIe 3.1 Controller with AXI

- Compliant with the PCI Express 3.1/3.0, and PIPE (16- and 32-bit) specifications

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode configurations

- Supports x16, x8, x4, x2, x1 at 8 GT/s, 5 GT/s, 2.5 GT/s speeds

- Supports AER, ECRC, ECC, MSI, MSI-X, Multi-function, P2P, crosslink, and other optional features

- Supports many ECNs including LTR, L1 PM substates, etc.