Multimedia IP for TSMC

Welcome to the ultimate

Multimedia IP

for

TSMC

hub! Explore our vast directory of

Multimedia IP

for

TSMC

All offers in

Multimedia IP

for

TSMC

Filter

Compare

34

Multimedia IP

for

TSMC

from

9

vendors

(1

-

10)

-

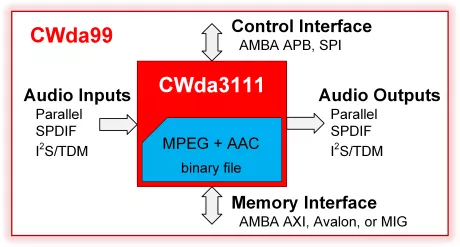

MPEG-1/2 + AAC Audio Decoder

- The MPEG-1/2+AAC Audio Decoder (CWda99) is an audio IP core for decoding up to 6 audio channels in real-time.

- This core contains the MPEG + AAC decoder software and the Coreworks processor based hardware audio engine platform (CWda3111).

-

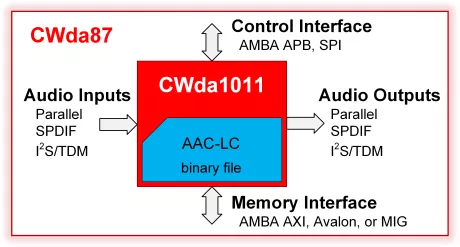

AAC-LC Audio Decoder

- The AAC-LC Audio Decoder (CWda87) is an audio IP core for decoding up to 6 audio channels in real-time.

- This core contains the AAC-LC decoder software and the Coreworks processor based hardware audio engine platform (CWda1011).

-

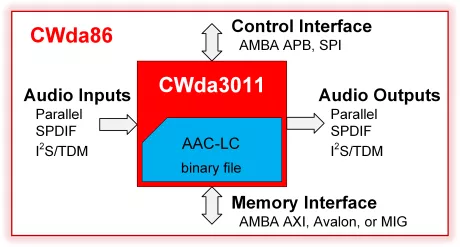

AAC-LC Audio Encoder

- The AAC-LC Audio Encoder (CWda86) is an audio IP core for encoding up to 6 audio channels in real-time.

- This core contains the AAC-LC encoder software and the Coreworks processor based hardware audio engine platform (CWda3011).

-

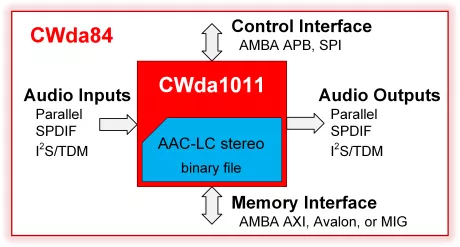

AAC-LC Stereo Audio Encoder

- The AAC-LC Stereo Audio Encoder (CWda84) is an audio IP core for encoding one stereo stream in real-time.

- This core contains the AAC-LC stereo encoder software and the Coreworks processor based hardware audio engine platform (CWda1011).

-

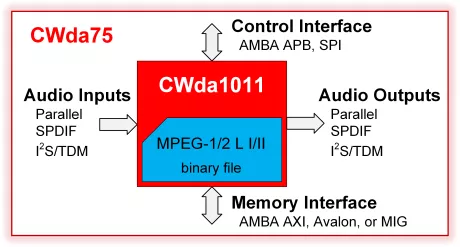

MPEG-1/2 – Layer I/II Audio Decoder

- The MPEG-1/2 – Layer I/II Audio Decoder (CWda75) is an audio IP core for decoding one audio stream in real-time(1).

- This core contains the MPEG-1/2 – Layer I/II decoder software and the Coreworks processor based hardware audio engine platform (CWda1011).

-

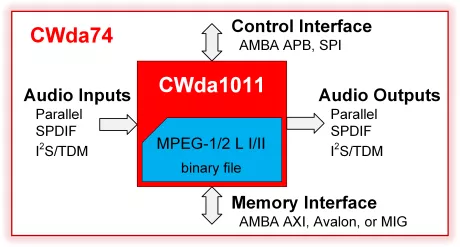

MPEG-1/2 - Layer I/II Audio Encoder

- The MPEG-1/2 – Layer I/II Audio Encoder (CWda74) is an audio IP core for encoding one audio stream in real-time.

- This core contains the MPEG-1/2 – Layer I/II encoder software and the Coreworks processor based hardware audio engine platform (CWda1011).

-

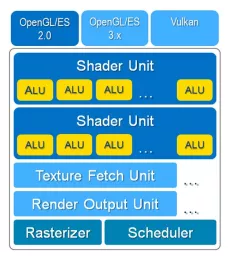

OpenGL ES 2.0 3D graphics IP core for FPGAs and ASICs

- D/AVE NX is the latest and most powerful addition to the D/AVE family of rendering cores.

- It is the first IP to bring 3D graphics OpenGL ES 2.0 rendering (with some ES 3.0 / 3.1 extensions) to the FPGA and SoC world and – with offline-shader compilers – even into MCUs or low-end MPUs with small amounts of memory and bare-metal or RTOS operation systems.

-

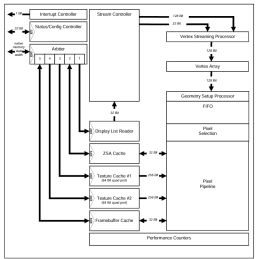

3D OpenGL ES 1.1 GPU IP core

- D/AVE 3D is cost-efficient IP core for 3D graphics applications.

- This core is available for FPGAs, ASICs and SOCs, specifically designed for the embedded, automotive and infotainment market with a big emphasis on flexibility both in hardware and the software.

-

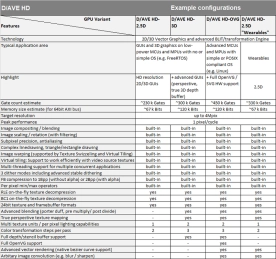

2.5D GPU

- The D/AVE HD 2.5D GPU family is an evolution of the D/AVE 2D family supporting high quality 2D and 3D rendering for displays up to 4K x 4K.

- Targeting modern graphics applications on high resolution displays in the Industrial, Medical, Military, Avionics, Automotive and Consumer markets, the D/AVE HD fixed-function 2.5D GPU core is designed to be fast with powerful functionality.

-

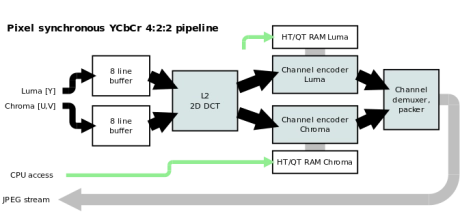

JPEG encoder

- Baseline JPEG compliant (ITU T.81), Motion JPEG

- Up to 12 bits depth possible (default: 8 bit)

- Super low latency (less than 1/10 of frame duration for rolling shutter cameras)

- Lossy compression by default

- Fully bit and cycle accurate co-simulation model available in Docker container